# BELETRXIVII (OLD) 26/11/12

AGJ-2nd half (k)-12-26

Con. 9445-12.

(OLD COURSE)

KR-2310

(3 Hours)

Total Marks: 100

- N.B.; (1) Question No. 1 is compulsory.

- (2) Attempt any four of the remaining six questions.

- (3) Assume suitable data wherever required and justify the same.

- 1. Answer the following questions (any five ) :-

20

- (a) Show that the zero locations of FIR filter occur at reciprocal locations.

- (b) Compare and contrast FIR and IIR filters.

- (c) What is the need for linear phase response in FIR filters? State the condition for FIR filter, to display linear phase characteristics.

- (d) How are gain and alternation related on linear and decibel scale? Illustrate the magnitude and phase characteristics of four classical filters.

- (c) Justify the statement 'Ideal filter characteristics are not realisable.'

- (f) Explain the characteristics of different window functions.

- 2. (a) Design a lowpass filter (FIR) with cut-off frequency of 5 KHz and sampling frequency 10 of 20 KHz using flamming window function. Assume N = 9.

- (b) Explain the impulse invariance (IIR) method of filter design in digital domain.

- 3. (a) Prove that  $S = \frac{2}{T} \left[ \frac{1 z^{-1}}{1 + z^{-1}} \right]$  and  $W = 2 \tan^{-1} \left[ \frac{\Omega T}{2} \right]$  in bilinear transformation. Explain 15

the mapping between the S-domain and Z-domain

(b) Check for linearity the following filter functions.

$$y(n) = x(n) -7x^{2}(n-1)$$

$y(n) = 3x(n-1)+3x(n+2)$

characteristics.

- 4. (a) Discuss the design steps for realisation of digital lowpass filter having Butterworth 10

- (b) Derive the expression for filter under N, M digital Butterworth filter realisation. 10

- 5. (a) Determine the coefficient of linear phase FIR filter of length N = 15 and having 10 frequency response as below.

$$H\left(\frac{2\pi k}{15}\right) = \begin{bmatrix} 1 & k = 0, 1, 2, 3\\ 0.4 & k = 4\\ 0 & k = 5, 6, 7 \end{bmatrix}$$

(b) Compare and contrast impulse invariance and bilinear transformation technique of 10 digital filter design (IIR).

#### Con. 9445-KR-2310-12.

- 6. (a) Explain in brief the design steps for FIR filter design using the frequency sampling 10 technique.

- (b) The frequency response of a filter has a form

10

$$H(w) = e^{-3jw} [1 + 0.4\cos 3w + 0.2\cos 2w + 0.2\cos w]$$

Find the impulse response of the system.

7. Write short notes on (any three) :-

20

- (a) Optimal linear phase FIR filter design

- (b) Discuss the design procedure of Bessel filter

- (c) Frequency transformation in digital domain

- (d) Chebyshev filter design

- (e) Design procedure of FIR filter design using Kaiser window

- (f) Quantization and limit cycle for first order and second order filter.

BE(III OLD) BILLX

Instrumentalian 17/ter (OLD COURSE)

71 2nd half-12-(h) JP Con. 8639-12.

(3 Hours)

Total Marks: 100

| N. | .В.:                     | <ol> <li>Question No. 1 is compulsory.</li> <li>Attempt any four questions out of remaining six questions.</li> <li>Figures to the right indicate full marks.</li> </ol>         |             |

|----|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1. | (a)<br>(b)<br>(c)<br>(d) | Explain PC based data acquisition system.  Derive the expression for strain guage factor.                                                                                        | 5<br>5<br>5 |

| 2. | (a)                      | Derive the expression for step response of second order system.                                                                                                                  | 10          |

| -  | (b)                      | Explain ultrasonic and electromagnetic flow meters.                                                                                                                              | 10          |

| 3. | (a)                      | Explain the concept of Virtual Instrumentation with its advantage, disadvantage and applications.                                                                                | 10          |

|    | (b)                      | Explain capacitive and inductive type of transducers.                                                                                                                            | 10          |

| 4. | (a)                      | Explain digital data acquisition system and also give advantage of digital DAS over Analog DAS.                                                                                  |             |

|    | (b)                      | Differentiate based on principles of working materials used, different specification, advantages and disadvantages of RTD, Thermo couple and thermistor temperature transducers. | 10          |

| 5. | (a)                      | What are different materials used for strain gauges? Explain different gauge circuits used in instrumentation system.                                                            | 10          |

|    | (b)                      | Short note on :— Data Logger.                                                                                                                                                    | 10          |

| _  | / <b>\</b> .             |                                                                                                                                                                                  | 10          |

| 6. | (a) (b)                  |                                                                                                                                                                                  | 10<br>10    |

|    | (0)                      | in the characteristics of nanodavers and private emberreanten or nanodavers.                                                                                                     |             |

| 7. | (a)                      | What different types of pressure sensors are used in instrumentation system? Explain any one method.                                                                             | 10          |

|    | (b)                      | Short note on: Piezoelectric Transducers.                                                                                                                                        | 10          |

## B.E (ETER) VII OLD Dec-2012

47-p3-d-upq-SH KSL12 C

Con. 10328-12.

### (OLD COURSE)

KR-2484

5

5

(3 Hours)

Total Marks: 100

- N.B. :(1) Question No. 1 is compulsory.

- (2) Solve any four from remaining six questions.

- (3) Assume suitable data if necessary.

- 1. (a) What is Velocity Saturation? How does it affect the I–V characteristics of a short channel MOSFET.

- (b) Compare CMOS NAND with CMOS NOR gate which requires less area. 5

- (c) Compare Burried and Butting Contacts.

- (d) Draw stick diagram for CMOS inverter. 5

- 2. (a) Calculate the threshold voltage  $V_{TO}$  at  $V_{SB} = 0$ , for a polysilicon gate 10 N-Channel MOS transistor, with following parameters:—

Substrate doping density  $N_A = 10^{16} \text{ cm}^{-3}$

Polysilicon gate doping density  $N_D = 2 \times 10^{20} \text{ cm}^{-3}$

Gate oxide thickness tox =  $300 \,\text{Å}$

Oxide interface fixed charge density  $N_{OX} = 4 \times 10^{10} \text{cm}^{-2}$

(ni =  $1.45 \times 10^{10}$ /cm<sup>3</sup>,  $\varepsilon o x = 0.345 \times 10^{-12}$  F/cm<sup>2</sup>

$$\varepsilon si = 1.035 \times 10^{-12} \text{ F/cm}^2$$

- (b) Explain the short channel effect with respect to the following points:— 10

- (i) Subthreshold conduction

- (ii) Channel length modulation effect

- (iii) Drain induced barrier lowering

- (iv) Velocity saturation and mobility degradation.

- 3. (a) Describe various types of load which can be used for-inverter gives their advantages and limitation.

- (b) Describe the limitation of a scaling of a MOS device. Derive the gate delay and power dissipation change after scaling in terms of scaling factor.

- 4. (a) In the inverter circuit what is meant by Zpu/Zpd. Derive the required ratio between Zpu/Zpd if an n MOS inverter is to be driven from another inverter.

- (b) Implement the following Boolean function in CMOS logic.

$$Y = A (D + E) + BC$$

Draw the stick diagram for the circuit.

| Con. | 10328 | -KR | -2484 | -12 |

|------|-------|-----|-------|-----|

|------|-------|-----|-------|-----|

2

5. (a) Explain Ion implantation and compare it with diffusion clearly stating the advantages and disadvantages.

(b) Draw the stick diagram and mask layout using λ based design rules for two i/p CMOS NAND gate with a pull up to pull down ratio as 4: I.

6. (a) Explain the latch up in CMOS. What are the remedies to avoid it.

(b) Design 4: I multiplexer using NMOS pass transistor. Also draw the stick diagram.

7. Write short notes on any two of the following:—

20

(a) VHDL in VLSI design

\_\_\_\_\_

Power dissipation in CMOS inverter Photolithography in IC fabrication.

### BEITTEX [VII (Old) 12/12/12 Digiral Communication

D Scan Pra 1-40 Con. 10860-12.

(OLD COURSE)

KR-2637

(3 Hours)

Total Marks: 100

- N.B. (1) Question No. 1 is compulsory.

- (2) Attempt any four questions out of remaining six questions.

- (3) Assume any suitable data if required.

- 1. (a) The channel capacity is given by  $C = B \log_2 \left( \frac{S}{1 + N} \right)$  in the presence of which gaussian noise with a constant signal power the channel capacity reaches its

upper limit with increase in the bandwidth B. Prove that this upper limit of C is given by  $C_{\infty} = 1.44 \, \frac{\text{S}_{\text{Nln}}}{\text{Nln}}$

(b) State and prove Central Limit Theorem.

10

(a) Why is differential encoding used in PSK systems?

- 5

- (b) Explain the advantage of gray coding of the i/p to QPSK system.

- 5

(c) Differentiate source coding line coding and error delation codes.

10

3. Consider (7, 4) code whose generator matrix is-

20

$$G = \begin{bmatrix} 1 & 1 & 1 & 1 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 & 0 & 1 & 0 \\ 1 & 1 & 0 & 0 & 0 & 0 & 1 \end{bmatrix}$$

- (a) Find all the codewords of code.

- (b) Find if the parity check matrix of the code

- (c) Compare the syndrome for the received vector 1101101. is this a valid code vector?

- (d) What is the error correcting capability of the code?

- (e) What is the error delecting capability of the code?

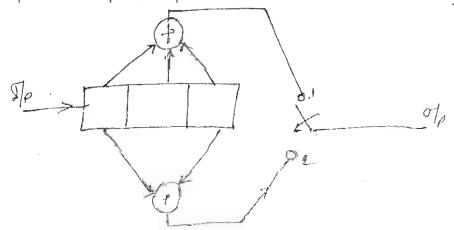

- 4. (a) A convolution encoder shown in **Figure** allows the shift of 2 message bits at a time 15 what will be the constraint length and rate efficiency of the code.

Initially consider that the register contains all zeros. What will be the code sequence if the <sup>1</sup>/p data sequence is 100110?

(b) Compare digital modulation techniques.

#### D\_Scan Pra 1 41 Con. 10860- KR-2637-12.

- -5

- 5. (a) What is offset and non offset QPSK explain indetail?

6.

(b) What is inter symbol interference? How does it a rise in a communication system?

Explain a system which will eliminate the same with the help of block diagram and

10

10

10

10

20

with sketches.

The Rayleigh density function is given by-

- $f(\mathbf{x}) = \begin{cases} xe^{-\mathbf{x}^2/2} & \mathbf{x} \ge 0\\ 0 & \mathbf{x} < 0 \end{cases}$

- (i) Prove that the f(x) satisfies fundamental properties of probability density function.(ii) Find the distribution function f(x).

- (ii) Find the distribution function f(x).(b) Explain with neat block diag direct sequence spread spectrum technique.

- Write short notes on :-

- (a) Processing gain

- (b) Jamming margin(c) Eye pattern

- (d) Viterbi decoding.

B.F. [ Electron (S) Sem-VII (Old) Flective-I mi (50000000 Parter 5:)8 fem Design 17/12/12

Con. 10990-12.

(OLD COURSE)

(3 Hours)

[Total Marks: 100

Question Number 1 is compulsory. Solve any 4 from remaining 6 questions Draw neat diagrams wherever necessary. 1. a. Explain any one Read Scenario explaining the MESI cache consistency (10) model in the Pentium. b. Explain the reasons for the Green Nature of the PCI Bus. (10)2. a. Explain with a neat diagram the Code cache organization of the Pentium. (10) Explain the directory entry fields. b. Explain with a neat diagram a read transaction followed by a write (10)transaction on the PCI bus. 3. a. Draw State diagram of Pentium Bus cycles. Explain each state and cause (10) for the transition. b. Explain the interrupts of the Pentium Processor. (10)4. a. Explain SCSI Bus protocol in detail. (10)b. Describe pipelined and non-pipelined bus cycles. in the Pentium (10) 5. a. Explain floating-point instruction execution stages in Pentium processor. (10)b. Explain the following: i. Latency timer in PCI Bus. (10)ii. Zone Bit recording in IDE 6. a. Explain in detail the function of the two prefetch queues in the Pentium (10)processor. b. Explain IDE protocols. (10)7. Write short notes on: (20)a. CHS and LBA addressing in IDE. b. USB transfers. c. Plug and Play feature of PCI.

d. Split-Line Access mechanism in Pentium.

B. E(E/E/27201168) Sem-VII (0/d) E/ergins - I Wisologs communication

27: 2nd half.12-shilpa(d)

(e) CT2.

Con. 8709-12.

### (OLD COURSE)

**KR-3168**

(3 Hours) [Total Marks: 100 N.B.: (1) Question No. 1 is compulsory. (2) Attempt any four questions out of remaining six questions. (3) Figures to the right indicate full marks. 1. (a) What is frequency reuse concept? 5 (b) Define reflection, diffraction and scattering, the three basic propogation mechanisms 5 in mobile communication. (c) Differentiate between fast fading and slow fading. 5 (d) Write a note on DECT. 5 2. (a) Explain multipath fading. What are the different physical factors which influences small scale fading? (b) For two-ray ground reflection model, derive the expression for received power, 10 Pr (d) at a distance 'd' from the transmitter. 3. (a) Explain G.S.M. Architecture and give radio air interface specifications (for GSM). 10 (b) What are architectural methods for capacity expansion in cellular communications? 10 4. (a) Describe knife edge Diffraction model with example. 10 (b) What are the features and services that has been standardized in cDMA? .10 5. (a) Explain with neat diagram, the functions of each block in detail for signal 10 processing in G.S.M. (b) Explain speech channel coding and inter leaving used in USDC systems. 10 6. (a) If 20 MHz total spectrum is allocated for a duplex wireless cellular system and each simplex channel has 20 KHz RF bandwidth find :-(i) The no. of duplex channels (ii) The total no. of channel for cellsite if N = 4, cell reuse is used. (b) Explain CDPD network Architecture. 10 20 7. Write short notes (any four):-(a) GSM Frame structure (b) Cell dragging (c) GPRS (d) Subscriber Identity module