# SECENTUS SEMI: III (CBSGes) NWM-DEC 2013 16:2nd half.13-Avi(at) SEMI: III (CBSGes) NWM-DEC 2013 Digstal Eleuthonies 4/12/13

Con. 8622-13.

GX-12122

(3 Hours)

[Total Marks: 80

N.B.: (1) Question No. 1 is compulsory.

(2) Out of remaining questions, attempt any three questions.

Assume suitable additional data if required.

(4) Figures in brackets on the right hand side indicate full marks.

| 1.    | (A)        | Compare combinational circuits with sequential circuits.                                                                                                                                                                                                                                                                                                                                                         | (05) |

|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|       | <b>(B)</b> | Compare TTL with CMOS logic families.                                                                                                                                                                                                                                                                                                                                                                            | (05) |

|       | (C)        | Compare SRAM with DRAM.                                                                                                                                                                                                                                                                                                                                                                                          | (05) |

|       | (D)        | Compare FPGAs with CPLDs.                                                                                                                                                                                                                                                                                                                                                                                        | (05) |

| 2.    | (A)        | State and prove De Morgan's theorem.                                                                                                                                                                                                                                                                                                                                                                             | (10) |

|       | <b>(B)</b> | Using Quine McClusky method, minimize the following:                                                                                                                                                                                                                                                                                                                                                             |      |

|       |            | $F(A,B,C,D) = \sum_{F} m(0,1,3,7,8,9,11,15,22,24,27) + d(6,16).$                                                                                                                                                                                                                                                                                                                                                 | (10) |

| 3.    | (A)        | Implement the following Boolean equation using single 8:1 MUX and few logic gates:                                                                                                                                                                                                                                                                                                                               | (10) |

|       |            | $F(A,B,C,D) = \sum m(0,1,3,4,8,9,15).$                                                                                                                                                                                                                                                                                                                                                                           |      |

|       | <b>(B)</b> | Write (32) <sub>10</sub> into its BCD code, and Ex-3 code.                                                                                                                                                                                                                                                                                                                                                       | (05) |

|       | (C)        | Implement $Y = A + \overline{BC}$ using only NOR gates.                                                                                                                                                                                                                                                                                                                                                          | (05) |

| 4.    | (A)        | Draw a neat circuit of BCD adder using IC 7483 and explain.                                                                                                                                                                                                                                                                                                                                                      | (10) |

|       | <b>(B)</b> | It is desired to develop the circuit for controlling a lamp on a staircase between 1 <sup>st</sup> and 2 <sup>nd</sup> floor of a building. Each floor is having only one switch. If a lamp is made 'ON' using switch of 1 <sup>st</sup> floor, one should be able to switch it 'OFF' using a switch of 2 <sup>nd</sup> floor and vice-versa. Design the circuit for the same. Write the VHDL code for the same. | (10) |

| 5.    | (A)        | What is shift register? Explain any one type of shift register. Give its application.                                                                                                                                                                                                                                                                                                                            | (10) |

|       | (B)        | Convert D type flip flop into T type flip flop.                                                                                                                                                                                                                                                                                                                                                                  | (05) |

|       | (C)        | Compare PAL with PLA.                                                                                                                                                                                                                                                                                                                                                                                            | (05) |

| 6.    | (A)        | Design a synchronous counter using D type flip flops for getting the                                                                                                                                                                                                                                                                                                                                             | (10) |

| :<br> |            | following sequence: $0-2-4-6-0$ . Take care of lockout condition.                                                                                                                                                                                                                                                                                                                                                |      |

|       | <b>(B)</b> | Explain any one application of Johnson counter.                                                                                                                                                                                                                                                                                                                                                                  | (05) |

|       | <b>(C)</b> | Draw the block diagram of internal architecture of XC9500 family CPLD and explain in brief.                                                                                                                                                                                                                                                                                                                      | (05) |

## 10/12/13 S. E. (EXTC) Som-III (Bas Electronic Instruments and Measurement

43: 2nd half.13-Avi(au)

Con. 8964-13.

GX-12161

|     |              | (3 Hours) [ Total Ma                                                                                                                                                                                                                                                                                                    | [ Total Marks : |  |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| N.  | B. :         | <ol> <li>Question No. 1 is compulsory.</li> <li>Out of remaining questions, attempt any three questions.</li> <li>Assume suitable additional data if required.</li> <li>Figures in brackets on the right hand side indicate full marks.</li> <li>Write your answers in Ink only.</li> </ol>                             |                 |  |

| . • | (A)          | Draw block diagram for generalized measurement system and explain its components.                                                                                                                                                                                                                                       | (05)            |  |

|     | <b>(B)</b>   | A strain gauge with gauge factor of 2 is fastened to a metallic member subjected to a stress of 1000 kg/cm <sup>2</sup> . The modulus of elasticity of the metal is 2*10 <sup>6</sup> kg/cm <sup>2</sup> . Calculate the percentage change in the resistance of the strain gauge? What is the value of poisson's ratio? | (05)            |  |

|     | <b>(C)</b>   | Explain the significance of X-1/2 digit displays.                                                                                                                                                                                                                                                                       | (05)            |  |

|     | ( <b>D</b> ) | Describe the various types of sweeps used in CRO                                                                                                                                                                                                                                                                        | (05)            |  |

| •   | (A           | Compare and explain different types of ADCs.                                                                                                                                                                                                                                                                            | (10)            |  |

|     | (B)          | Draw and explain the block diagram of general purpose CRO.                                                                                                                                                                                                                                                              | (10)            |  |

| •   | (A)          | Describe how $Q$ meter is used for the measurement of low impedance. What are the various sources of error in $Q$ meter?                                                                                                                                                                                                | (10)            |  |

|     | <b>(B)</b>   | Explain with neat diagram the working principle of LVDT. Give its application.                                                                                                                                                                                                                                          | (10)            |  |

| •   | (A)          | What is the basic principle of wave analyzer? Explain heterodyne type wave analyzer with application.                                                                                                                                                                                                                   | (10)            |  |

|     | <b>(B)</b>   | Explain the principle of operation of dual slope DVM.                                                                                                                                                                                                                                                                   | (10)            |  |

| •   | (A)          | Draw and explain the block diagram of DSO. Describe various modes of operation in it.                                                                                                                                                                                                                                   | (10)            |  |

|     | <b>(B)</b>   | Derive an expression for inductance measurement using Hay bridge.                                                                                                                                                                                                                                                       | (05)            |  |

|     | (C)          | Brief out classification of Errors in measurements.                                                                                                                                                                                                                                                                     | (05)            |  |

|     | (A)          | Brief out Classification of transducers.                                                                                                                                                                                                                                                                                | (07)            |  |

|     | <b>(B)</b>   | Explain electrodynamometer type wattmeter.                                                                                                                                                                                                                                                                              | (07)            |  |

|     | (C)          | Derive an expression for resistance measurement using Wheatstone bridge.                                                                                                                                                                                                                                                | (06)            |  |

(EXTC)

Circulto and Transmission Lines

Con. 9950-13.

GX-12194

(3 Hours)

Total Marks: 80

- Attempt Question No. I and any 3 from the remaining questions. In all 4 questions are to be attempted.

- All sub-questions of the same question should be answered at one place only in their serial, orders, and **not** scattered.

- Write everything in ink only. Pencil is not allowed.

- (4) Assume suitable data with justification if missing.

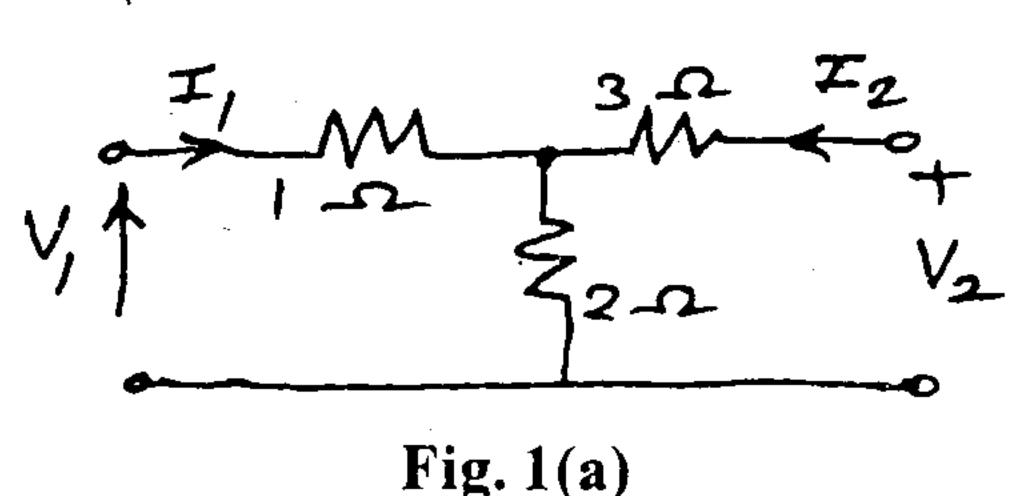

- Determine the the y-parameters of the network shown in Fig. 1(a).

- Test if  $F(s) = s^6 + 2s^5 + 3s^4 + 4s^3 + 3s^2 + 2s + 1$  is a Hurwitz polynomial.

- Both the coils connected in series have self inductance of 40 mH. The total inductance of (c) the circuit is found to be 120 mH. Determine the (i) mutual inductance between the coils and (ii) the coefficient of coupling.

- Find Foster I and II, and Cauer I and II circuits for the driving point admittance Y(s) = s + 1. 5 (d)

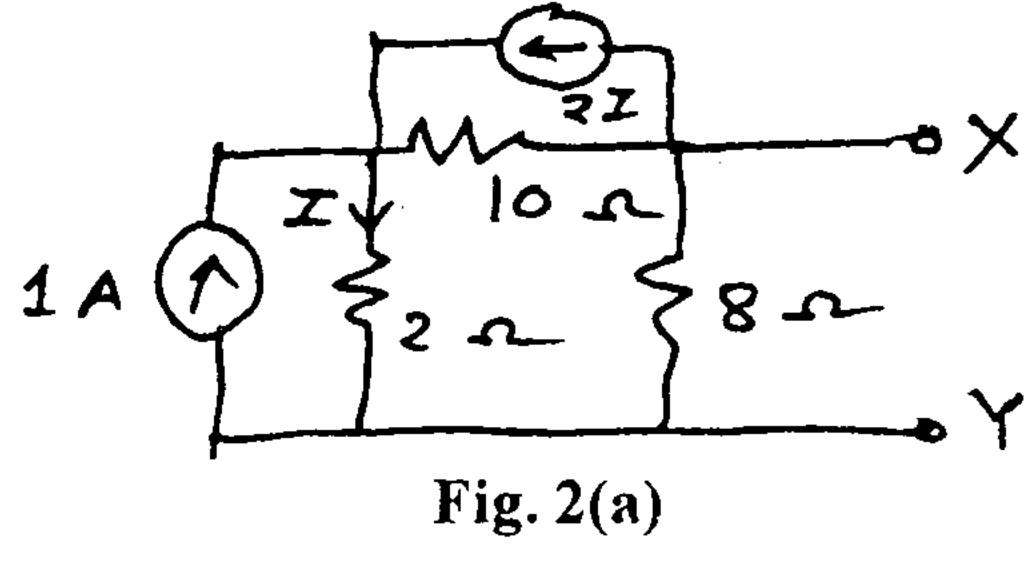

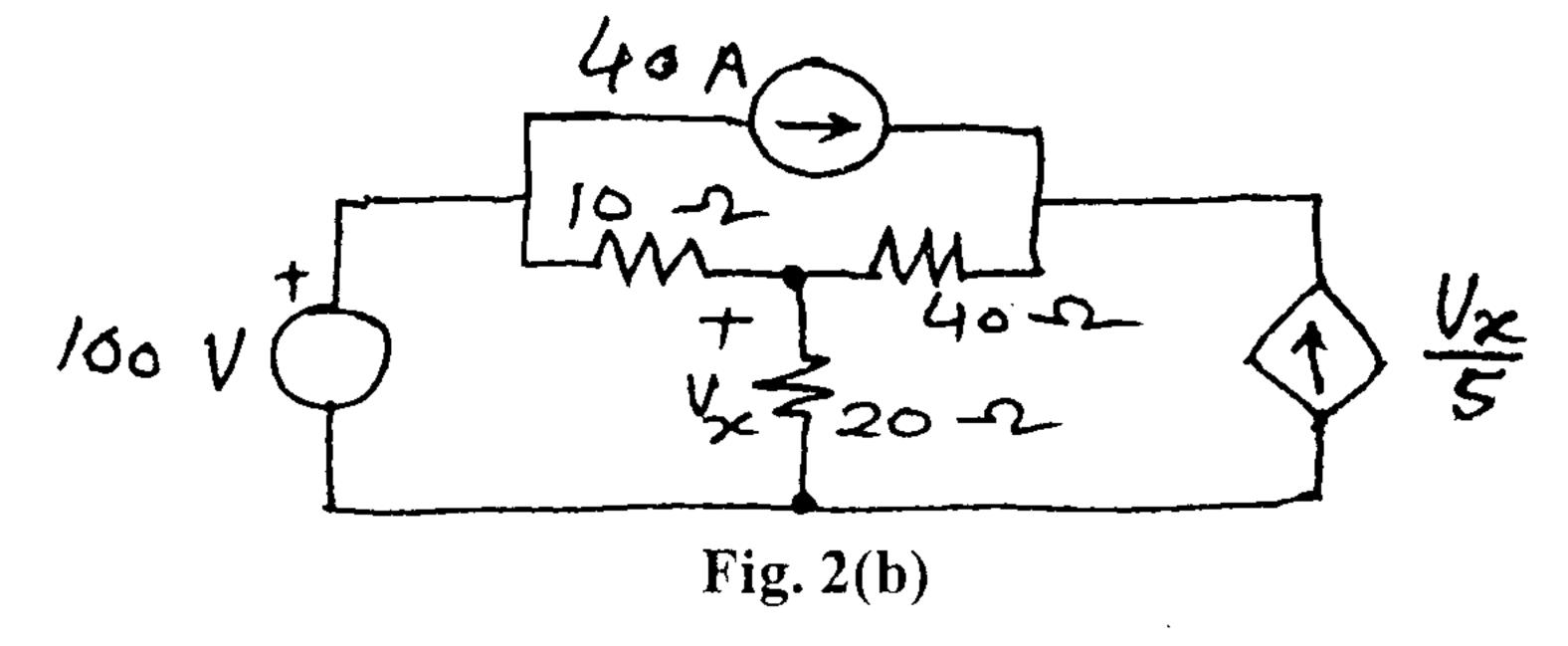

- Find the Thevenin equivalent across the terminals XY for the circuit shown in Fig.2(a) using 10 mesh matrix method.

Find the magnitude of the controlled source in the circuit shown in Fig.2(b) by node analysis. (b)

Check if the following polynomials are Hurwitz polynomials.

- (i)  $s^2 + 8$  (ii)  $(s + 2)^3$

#### Con. 9950-GX-12194-13.

- Synthesize the driving point function  $F(s) = \frac{\left(s^2 + 1\right)\left(s^2 + 9\right)}{s\left(s^2 + 4\right)}$  when F(s) is a driving point 10 (i) impedance (ii) admittance. Test if the circuit obtained are canonic.

- Find the voltage transfer function of a loaded two port network N in terms of the y-parameters (b)  $(y_{11}, y_{12}, y_{21}, y_{22})$  of the network N and load admittance  $Y_1$ .

- The parameters of a transmission line are: G = 2.25 mg/km,  $R = 65 \Omega/\text{km}$ , L = 1.6 mH/km, (c)  $C = 0.1 \mu F/km$ . Find  $Z_0$  and  $\gamma$  at a frequency of 1GHz.

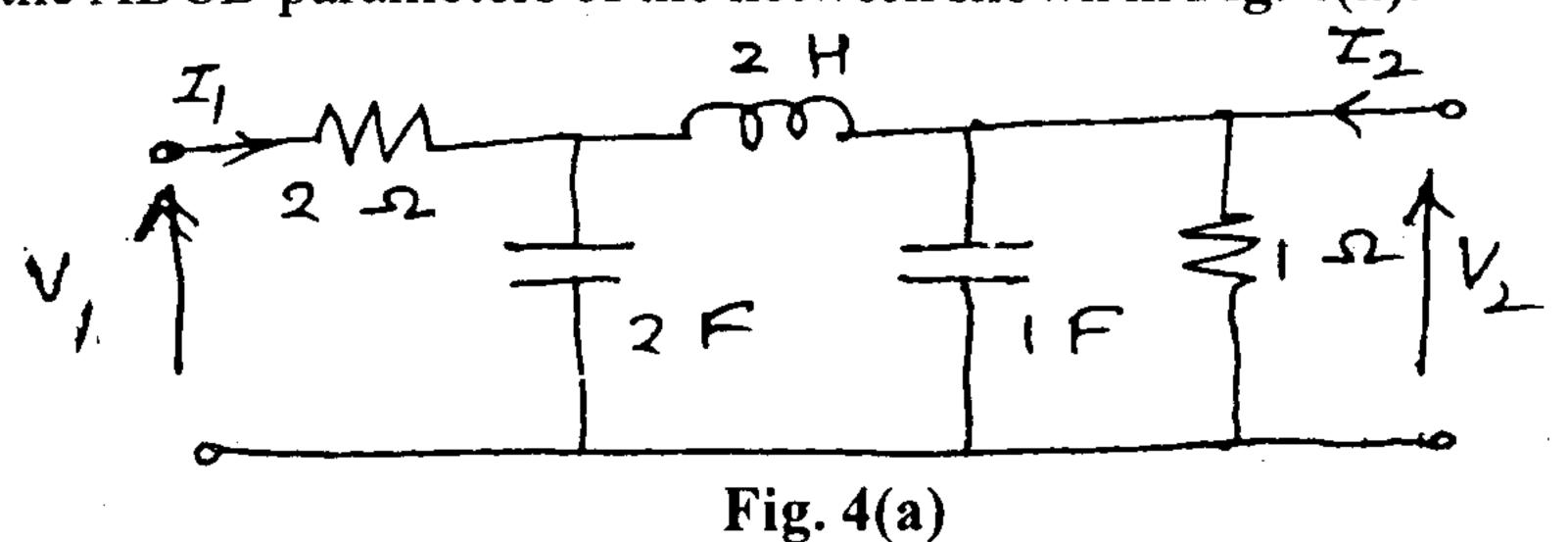

- Determine the ABCD parameters of the network shown in Fig. 4(a).

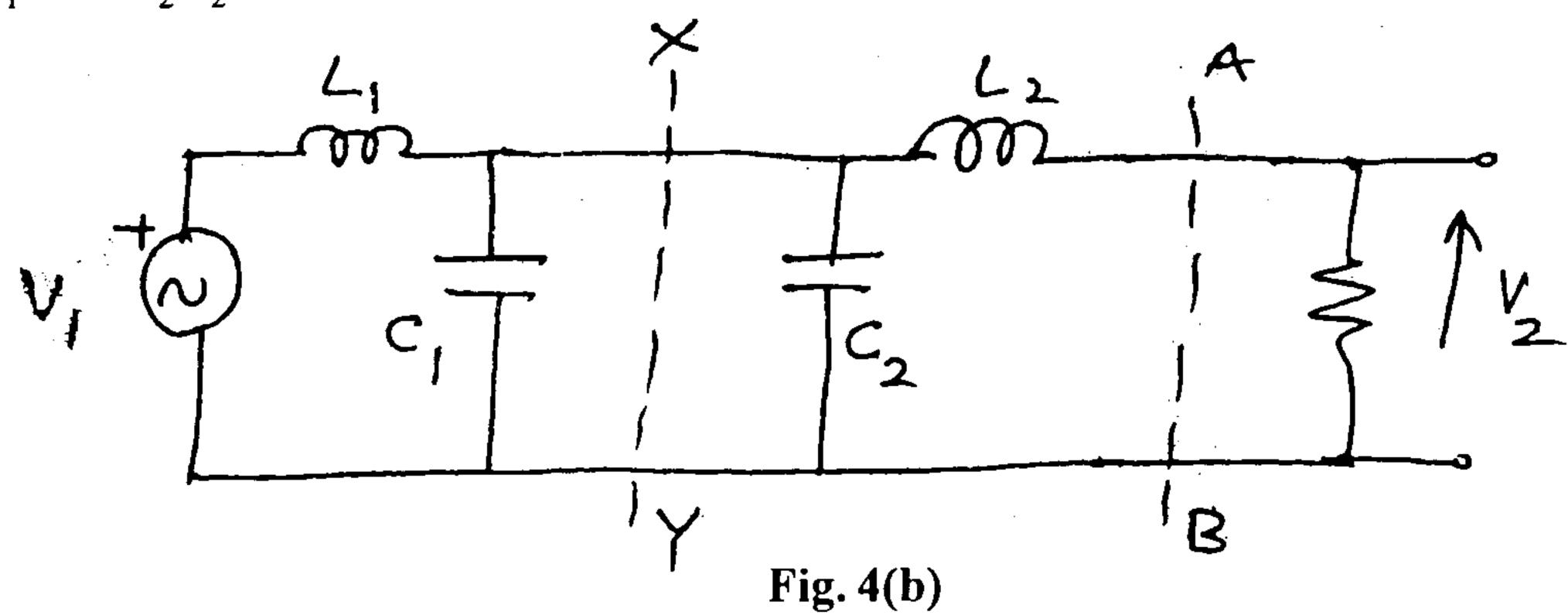

Determine the current transfer function for the circuit shown in Fig. 4(b) first finding the (b) Norton equivalent across XY and then Thevenin equivalent across AB under the condition  $\omega^2 L_1 C_1 = \omega^2 L_2 C_2 = 1.$

- (c) Test if  $F(s) = \frac{s^3 + 6s^2 + 7s + 3}{s^2 + 2s + 1}$  is a Positive Real Function.

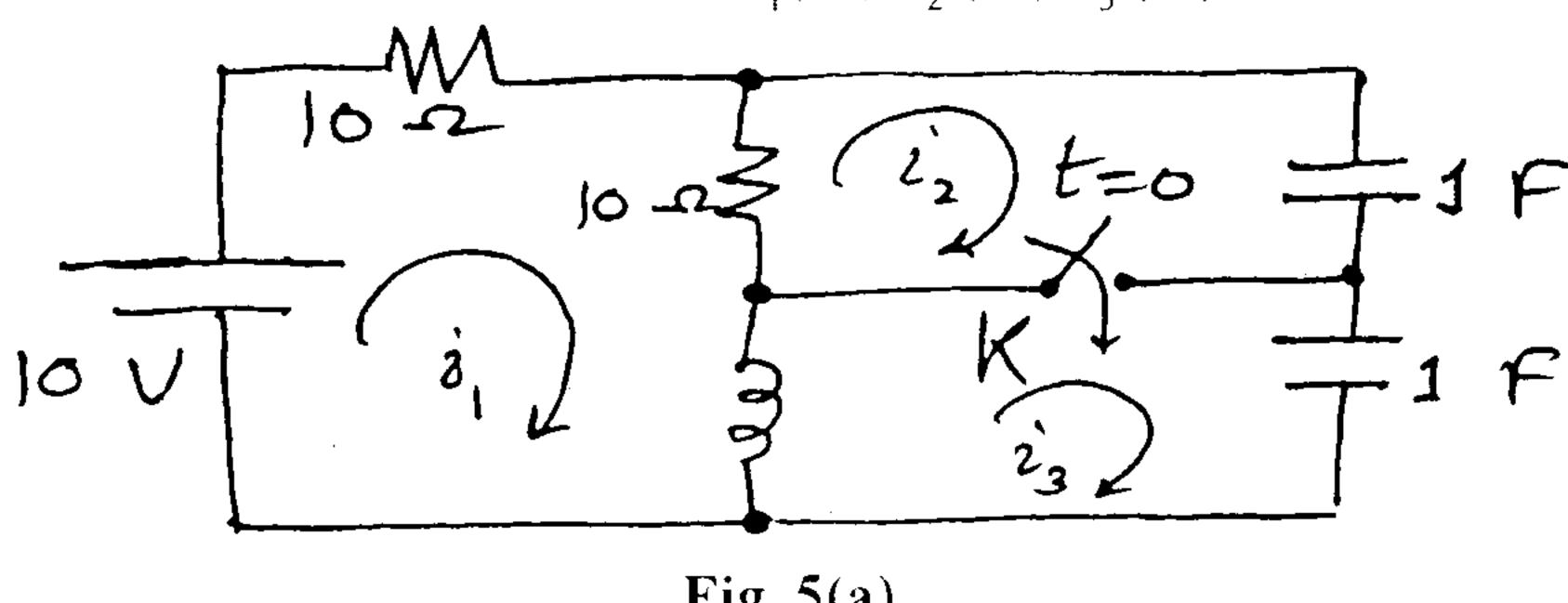

- The network shown in Fig. 5(a) attains steady-state with the switch K open. At t = 0, 10 the switch is closed. Determine  $i_1(0^+)$ ,  $i_2(0^+)$ ,  $i_3(0^+)$ .

Fig. 5(a)

TURN OVER

10

1

#### Con. 9950-GX-12194-13.

3

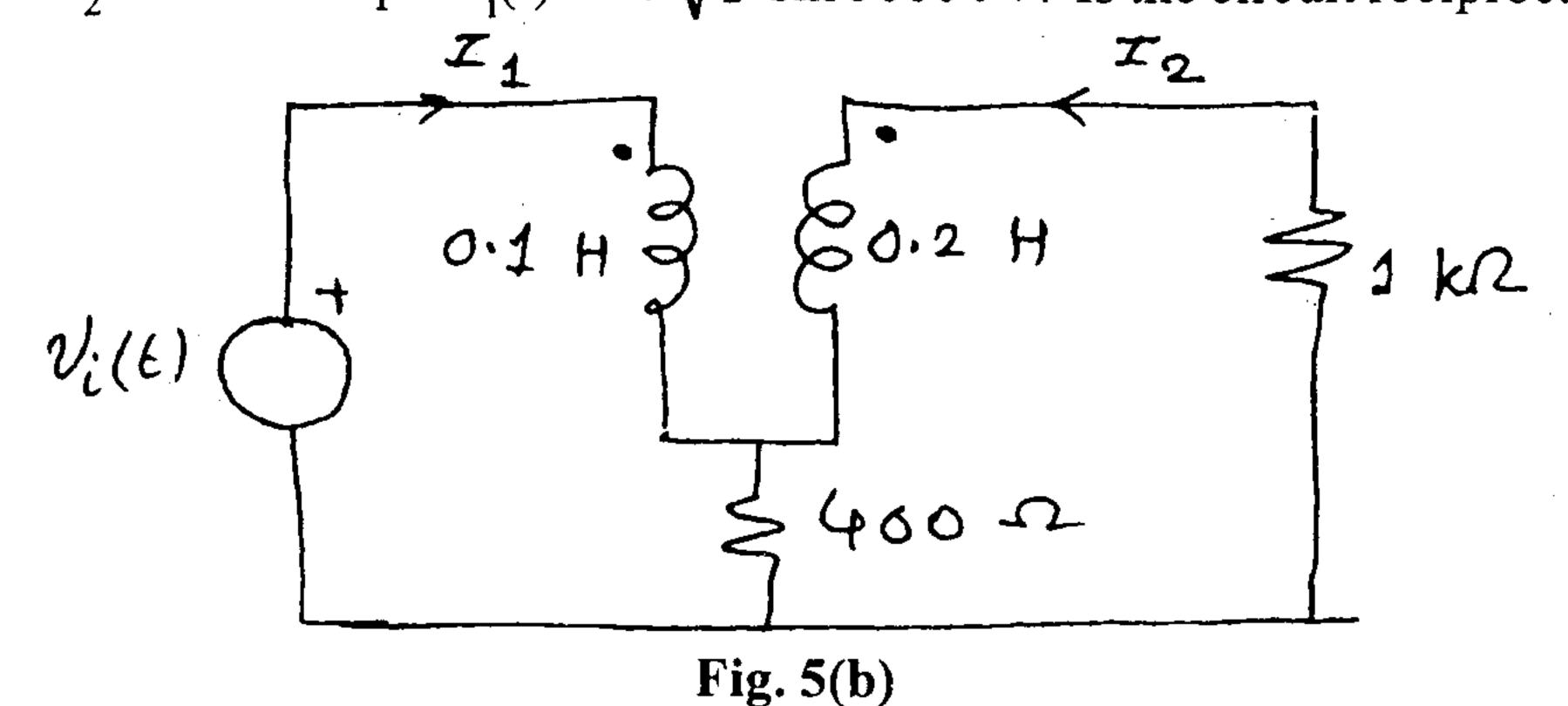

(b) In the circuit shown in Fig. 5(b) the two coupled coils have neglibible resistances. Find the current  $I_2$  when the input  $v_i(t) = 10 \sqrt{2} \sin 5000 t$  V. Is the circuit reciprocal?

(c) A generator of 1 V, 1 kHz supplies power to a 1000 km open wire terminated in  $Z_0$  having the following parameters.

$R = 10.4 \Omega/km$

L = 3.97 mH/km

$G = 0.8 \mu \sigma/km$

$C = 0.00835 \, \mu F/km$

Calculate the power delivered at the receiving end.

6. (a) Why is impedance matching required?

10

Draw the following normalized quantities on the Smith chart.

- (i)  $(1 + j1) \Omega$ ,

- (ii)  $(2-j1)\Omega$ ,

- (iii)  $(0.5) \Omega$ ,

- (iv)  $(j0.5) \Omega$

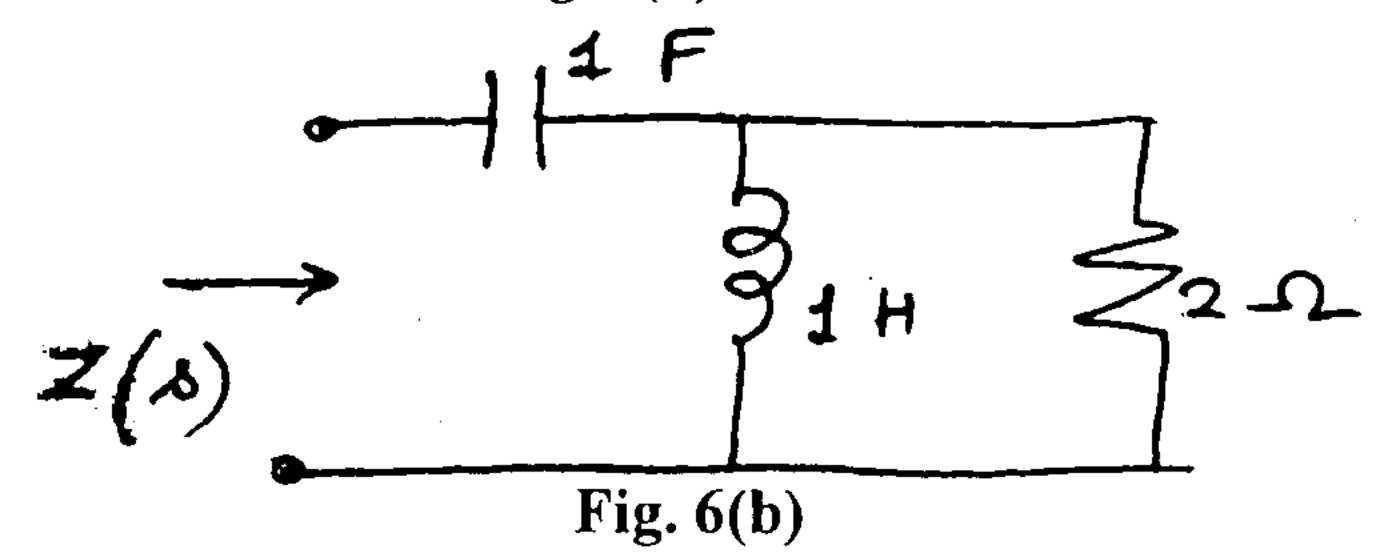

- (b) Find Z(s) for the circuit shown in Fig. 6(b).

•

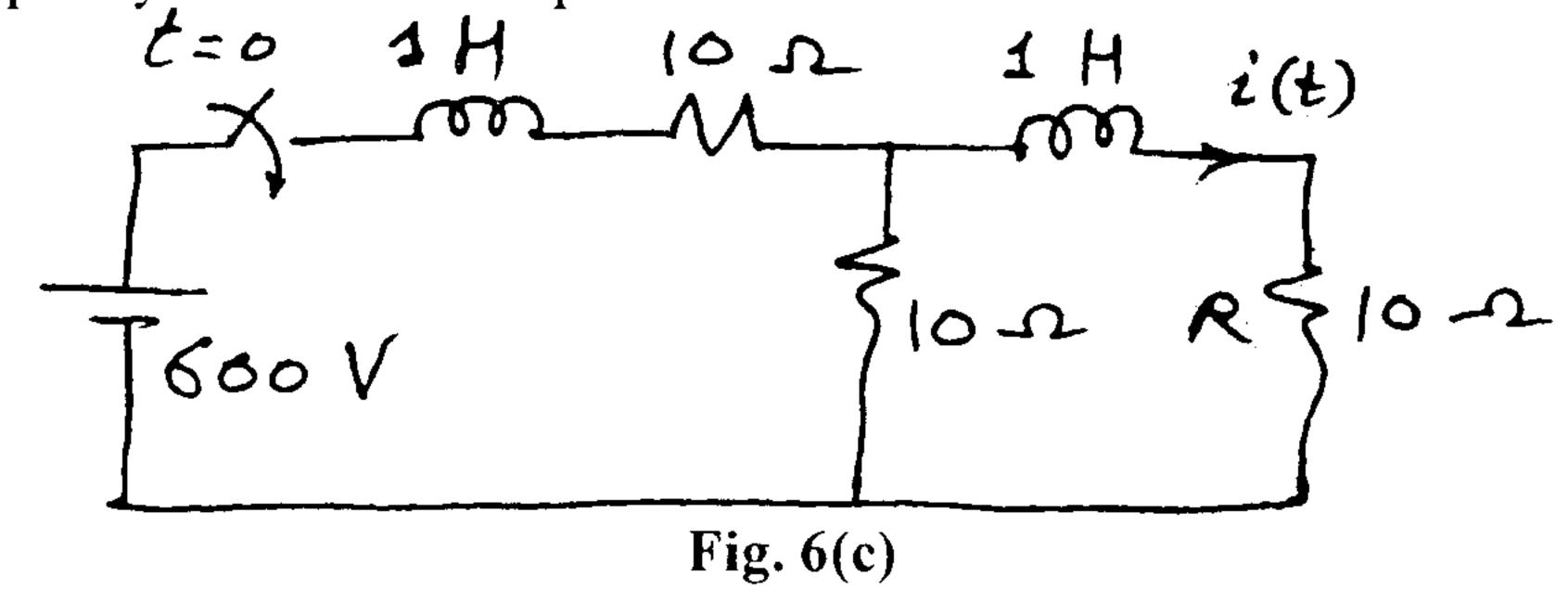

(c) Find current i(t) through R in the circuit shown in Fig.6(c) using Laplace transform. Why is the frequency domain method preferred to the classical time domain method?

Con. 7863-13.

GX-12049

(3 Hours)

[Total Marks: 80]

N.B.: (1) Question No. 1 is Compulsory.

- (2) Attempt any three questions out of remaining five.

- (3) Figures to the right indicate full marks.

#### Solve any five:

**20**

- (i) Draw switching characteristics of a diode and explain reverse recovery time.

(ii) Draw energy bond diagram of MUS capacitor in accumulation, depletion and inversion region for P-substrate.

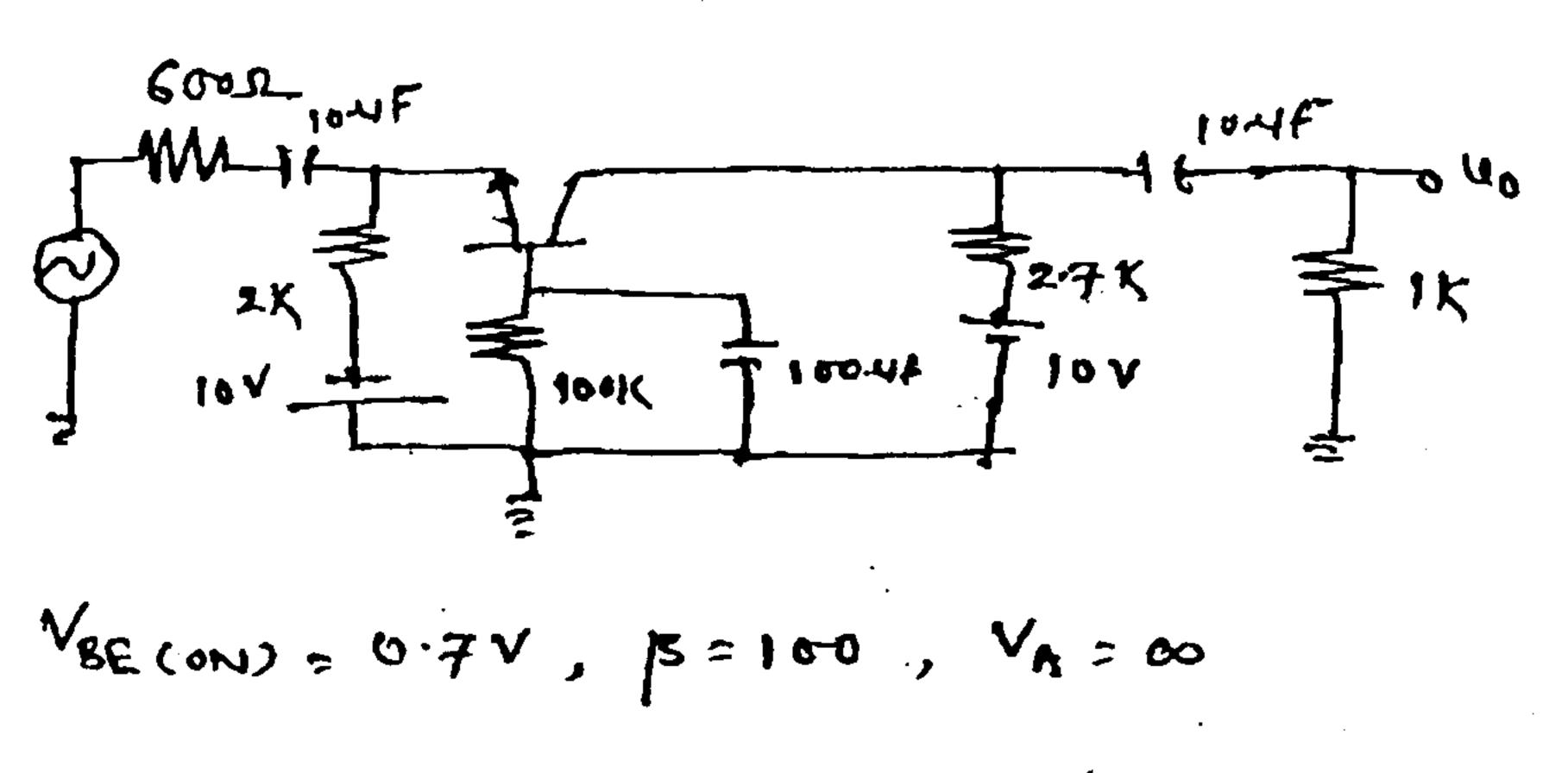

Draw the dc load line for above circuit.

(iv) Compare CE, CB and CC configuration.

(v)

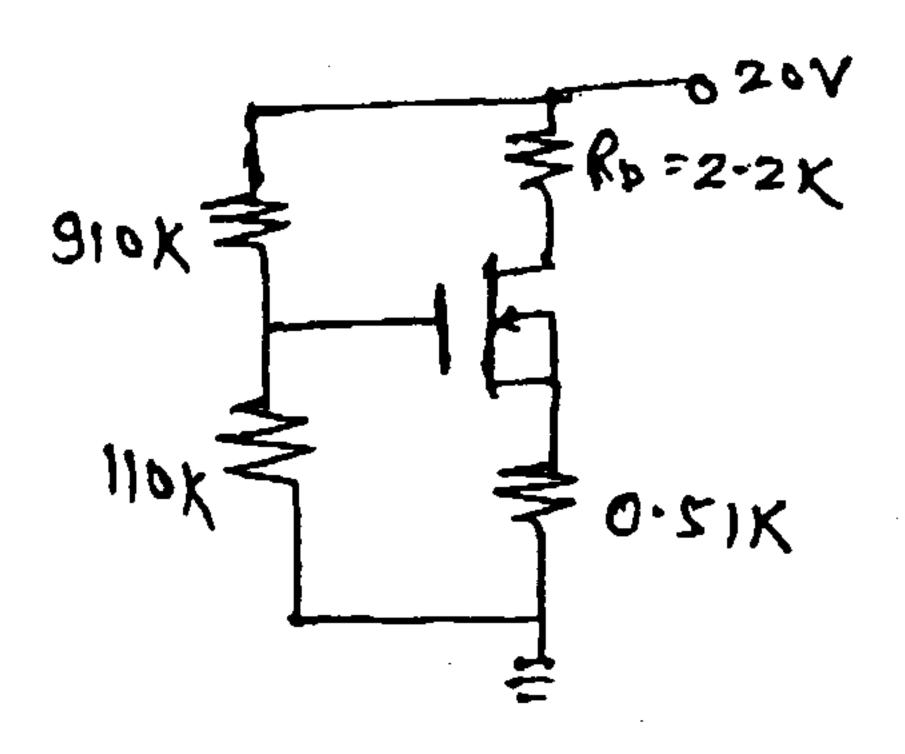

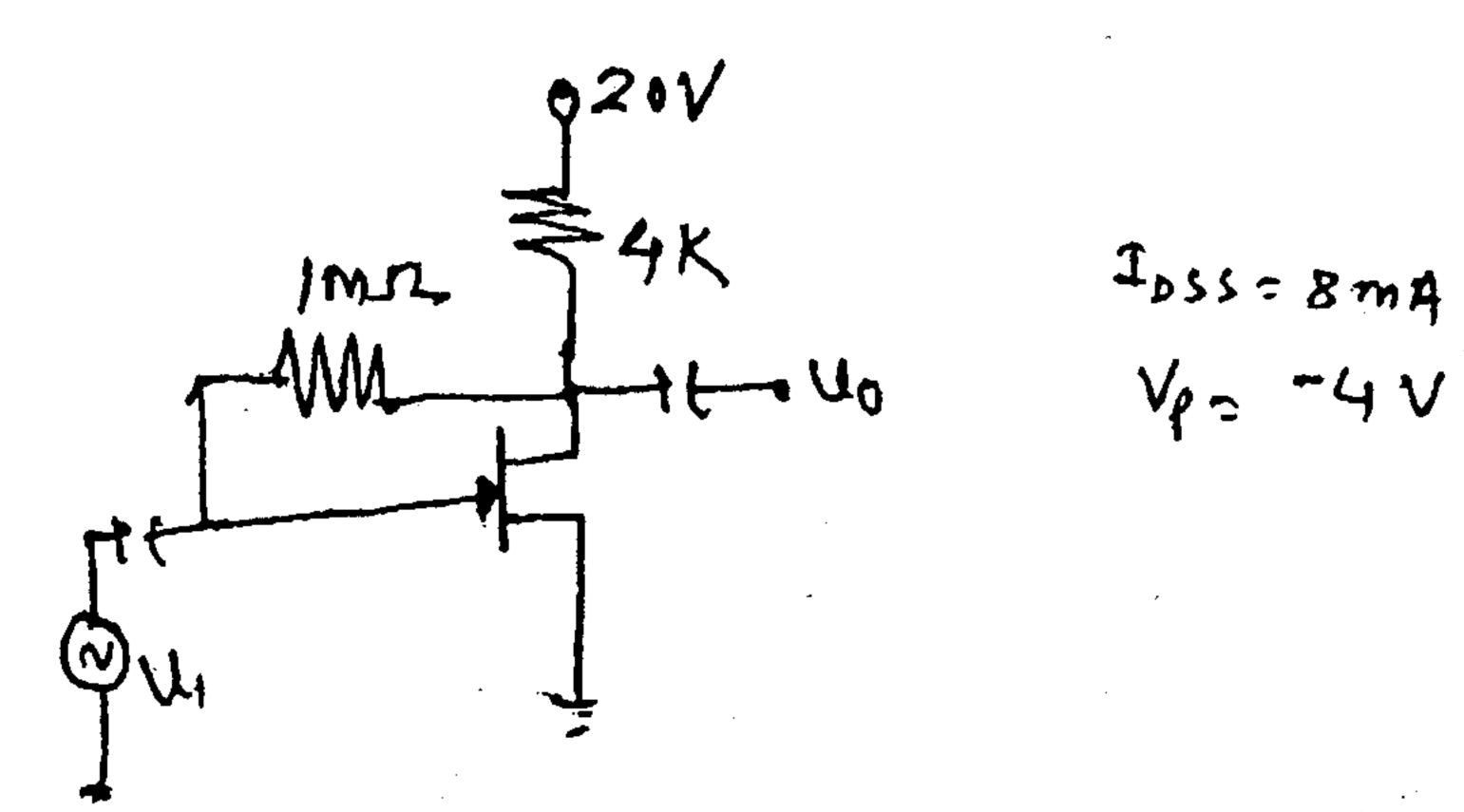

Obtain gm, ro and Av for the amplifier circuit shown in figure. In which region the device is operating? Justify.

(vi) State and explain Barkhausen's Criteria for oscillation.

(a) Obtain I<sub>DQ</sub>, V<sub>DSQ</sub>, V<sub>GSQ</sub> graphically.

8

(b) Derive he expression for frequency of oscillation for a transistorized (BJT) RC phase shift oscillator.

8

10

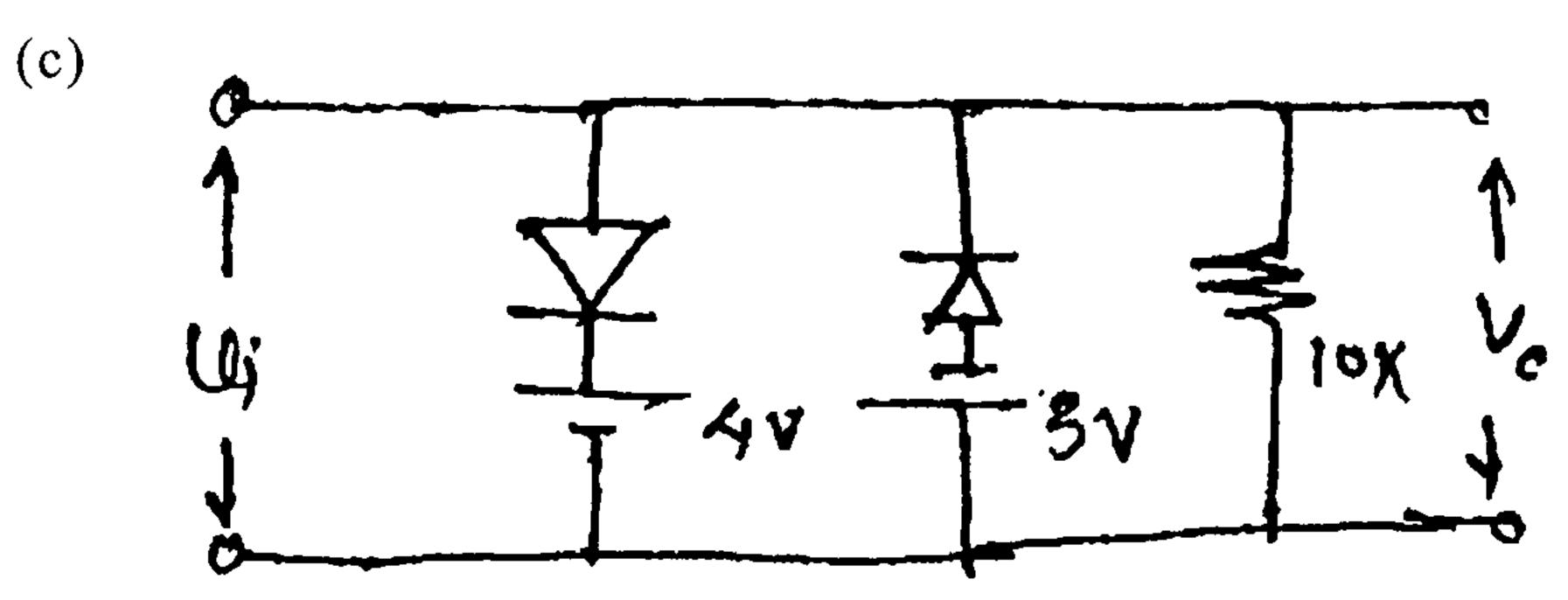

Obtain output for the clipper circuit shown in fig. If a sine wave of 15 sinwt is applied as an input. Assume practical diode with suitable cut in voltage.

3. (a)  $V_i \bigcirc V_i \bigcirc V_$

$$V_{TN} = 1V, K_n = 0.5 \text{ mA/V}^2. \lambda = 0.01 \text{ V}^{-1}$$

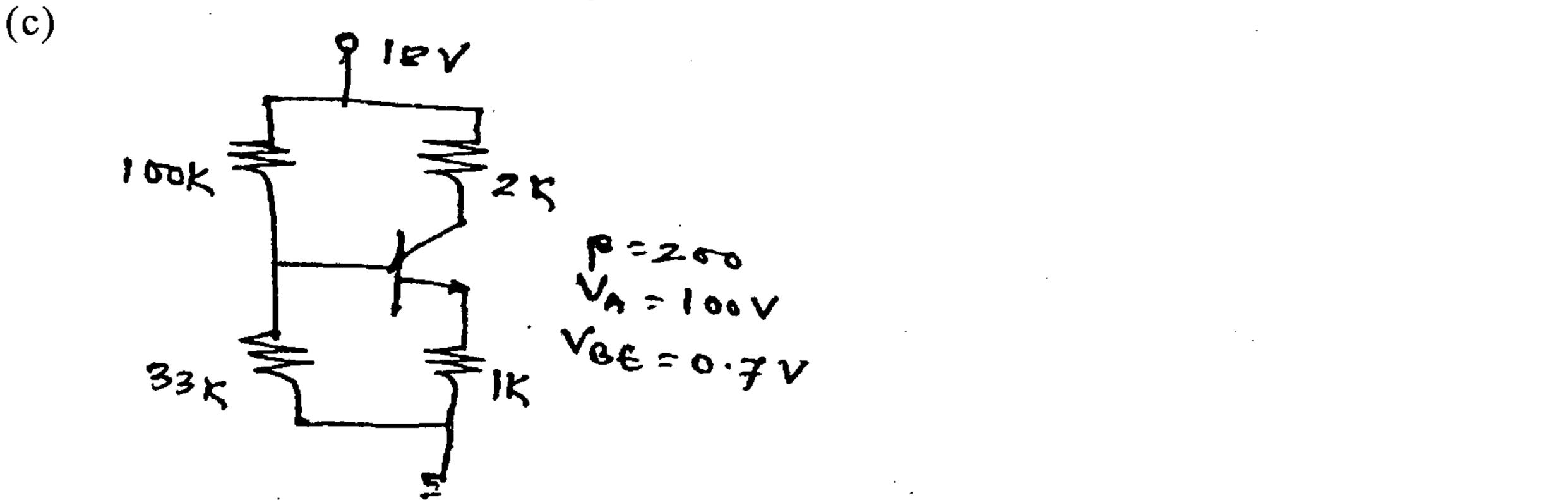

Determine  $V_{GSQ}$  and  $V_{DSQ}$ .

Also calculate volage gain, input and output resistance.

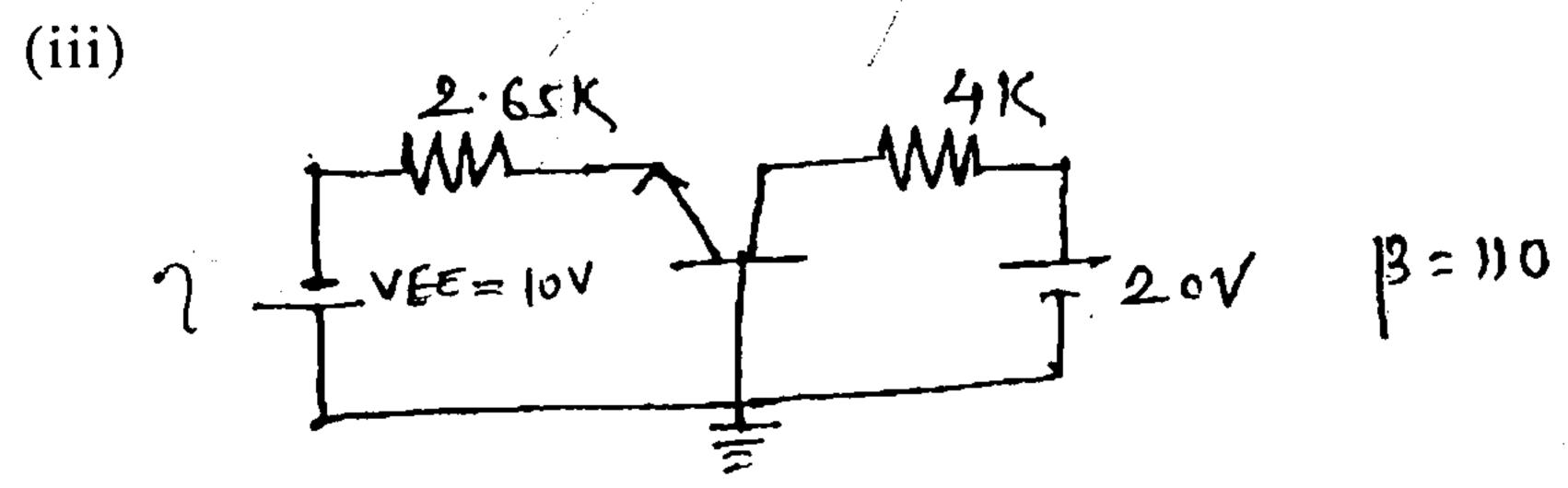

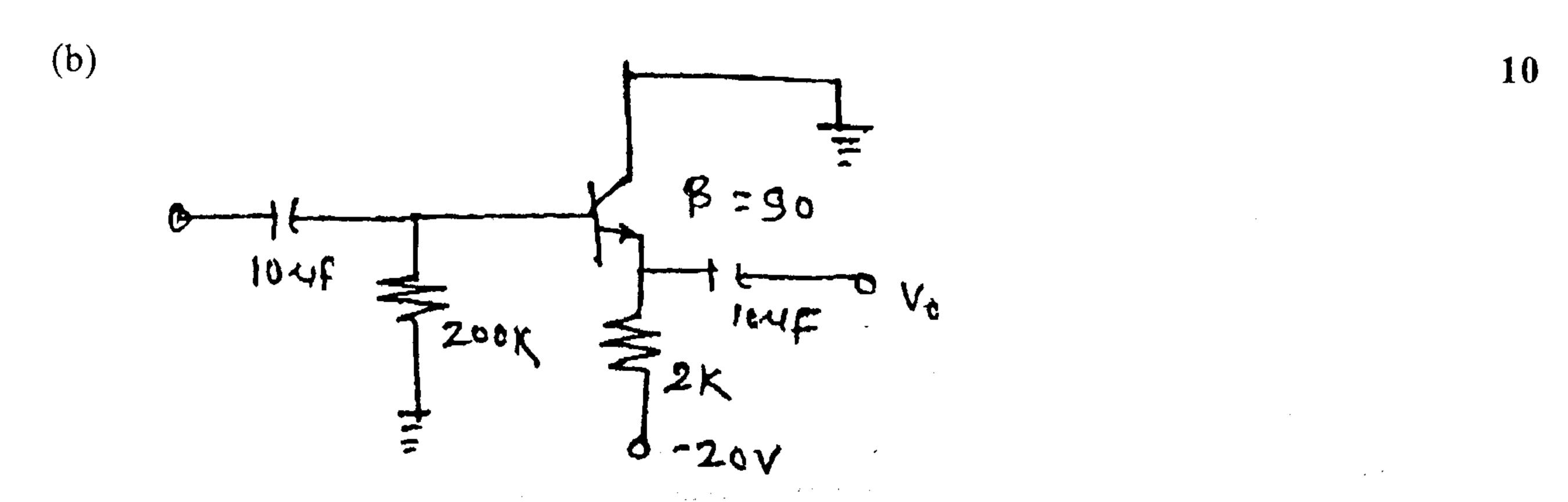

(b) Determine Ri, Ro, Av and gm for amplifier circuit shown in figure.

4. (a) Dervice the expression for Threshold Voltage for Enhancement type N-channel MOSFET. 1

Determin  $I_B$ ,  $I_C$ ,  $V_{CE}$ ,  $V_E$  and  $V_B$  and also  $S_{ICO}$  for the biasing circuit shown in figure.

5. (a) Explain graphical method to obtain to parameters of CE confirguration.

Calculate I<sub>DQ</sub>, V<sub>GSQ</sub> and V<sub>DSQ</sub>

Determine hybrid -  $\Pi$  parameters.

6. Write short note (any four):-

20

- (i) Small signal model of a diode

- (ii) Hybrid pi model of BJT

- (iii) Regions of operation of FET

- (iv) Crystal oscillator

- (v) Construction and operation of schottkey diode.

### S.E. ETRX 4 EXTC sem III CeB45) NOV-13 546:- AM-III. 29/11/13

Ash5-D:\Data-44

Con. 7885-13.

GX-12071

(3 Hours)

[Total Marks: 80

- N.B.:(1) Question no. 1 is compulsory.

- (2) Attempt any three questions out of the remaining five questions.

- (3) Figures to right indicate Full marks.

- 1. (a) Prove that real and imaginary parts of an analytic function F(z) = u + iv are 5 harmonic function.

- (b) Find fourier series for  $f(x) = |\sin x|$  in  $(-\Pi, \Pi)$ .

- (c) Find the Laplace transform of  $\int_{0}^{t} ue^{-3u} \sin 4u du$

- (d) If  $\overline{F} = xye^{2z} \stackrel{\wedge}{i} + xy^2 \cos z \stackrel{\wedge}{j} + x^2 \cos xy \stackrel{\wedge}{k}$ , find div  $\overline{F}$  and curl  $\overline{F}$ .

- 2. (a) Using Laplace transform, solve:- $(\mathbf{0}^{0} + 3\mathbf{0} + 2)\mathbf{y} = \mathbf{e}^{-2t} \sin t \text{ where } \mathbf{y}(0) = 0, \mathbf{y}'(0) = 0.$

- (b) Find the directional derivative of  $d = x^2 y \cos z$  at  $(1, 2, \frac{\Pi}{2})$  in the direction of 6

- (c) Find the fouries series expansion for  $F(x) = \sqrt{1 \cos x}$  in  $(0, 2\Pi)$ , Hence deduce 8 that  $\frac{1}{2} = \sum \frac{1}{4^{n^2} 1}$ .

- 3. (a) Prove the  $J_{\frac{3}{2}}(x) = \sqrt{\frac{2}{\Pi x}} \left\{ \frac{\sin x}{x} \cos x \right\}$ .

- (b) Evaluate by green's theorem,  $\oint_C (x^2ydx + y^3dy)$  Where C is the closed path formed 6 by y = x,  $y = x^2$

- (c) (i) Find Laplace transform of  $\frac{\cos bt \cos at}{t}$

### Con. 7885-GX-12071-13.

2

- (ii) Find Laplace transform of :-  $\frac{d}{dt}$   $\begin{bmatrix} \frac{\sin t}{t} \end{bmatrix}$

- 4. (a) Show that the set of functions  $\{\sin x, \sin 3x, \dots\}$  OR  $\{\sin (2n+1)x : n = 0, 1, 2, \dots\}$  is orthogonal over  $[0, \frac{\Pi}{2}]$ , Hence construct orthonormal set of functions.

- (b) Find the imaginary part whose real part is  $u = x^3 3xy^2 + 3x^2 3y^2 + 1$

- (c) Find inverse Laplace transform of:-

6

(i)

$$\log \left(\frac{s^2+4}{s^2+9}\right)$$

8

(ii)

$$\frac{s}{(s^2+4)(s^2+9)}$$

5. (a) Obtain half range sine series for  $f(x) = x^2$  in 0 < x < 3.

6

(b) A vector field  $\overline{F}$  is given by  $\overline{F} = (x^2 - yz)\hat{i} + (y^2 - zx)\hat{j} + (z^2 - xy)\hat{k}$  is irrotational and Hence find scalar point function  $\phi$  such that  $\overline{F} = \nabla \phi$

•

- (c) Show that the function  $V = e^{x}$  (xsiny + ycosy) satisfies Laplace equation and find its corresponding analytic function and its harmonic conjugate.

- By using stoke's theorem, evaluate  $\oint_C \left[ (x^2 + y^2)\hat{i} + (x^2 y^2)\hat{j} \right] dr$  where 'C' is the boundary of the region enclosed by circles  $x^2 + y^2 = 4$ ,  $x^2 + y^2 = 16$ .

- (b) Show that under the transformation  $w = \frac{z-4z}{4z-2}$  the circle |z| = 1 in the z-plane is transformed into a circle of unity in the w-plane.

- (c) Prove that  $\int J_3(x) dx = \frac{-2J_1(x)}{x} J_2(x)$ .