(3 Hours)

[ Total Marks: 100

|           | <ul> <li>N. B.: (1) Question No. 1 is compulsory.</li> <li>(2) Attempt any four questions out of remaining six.</li> <li>(3) Figures to the right indicate full marks.</li> <li>(4) Assume suitable data if required but justify the same.</li> </ul>                                                                                                                                                   |    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.        | <ul> <li>Attempt the following:— <ul> <li>(a) How a constant v/f control is superior to the stator voltage control?</li> <li>(b) Give the performance comparison of VSI and CSI.</li> <li>(c) Discuss the different factors for selection of battery for UPS.</li> <li>(d) Give the comparison between dual converter operating in non circulating and circulating current mode.</li> </ul> </li> </ul> | 20 |

| 2.        | <ul> <li>(a) With the help of circuit diagram and associated waveforms, explain the principle of operation of type C chopper.</li> <li>(b) Explain multiple pulse width modulation as used in DVM invertors.</li> </ul>                                                                                                                                                                                 | 10 |

|           | (b) Explain multiple pulse width modulation as used in PWM inverters.                                                                                                                                                                                                                                                                                                                                   | 10 |

| 3.        | (a) Explain with neat diagram the slip power recovery technique to control the speed of 3 phase slip ring induction motor above and below the synchronous speed. State the advantages of this technique.                                                                                                                                                                                                | 10 |

|           | (b) Explain with neat diagram and waveforms the operation of flyback converter.                                                                                                                                                                                                                                                                                                                         | 10 |

| <b>4.</b> | (a) A separately exicted D.C. motor operating from a single phase half controlled bridge rectifier at a speed of 1400 rpm. has an input voltage of 330 sin 314 t and a back emf of 80V. The SCR's are fired symmetrically at $\alpha = 30^{\circ}$ in every half cycle and the armature has a resistance of 4 $\Omega$ . Calculate the average armature current and the motor torque.                   | 10 |

|           | (b) Discuss the working of load commutated chopper with associated voltage and current waveforms. Show voltage variation across each pair of SCR's as a function of time.                                                                                                                                                                                                                               | 10 |

| 5.        | (a) Explain with neat diagram and waveforms the working of parallel inverter. What is the need for feedback diodes and pulse train for firing of SCR's.                                                                                                                                                                                                                                                 | 10 |

|           | (b) Discribe the working of a single phase full converter fed separately excited D.C. motor with circuit diagram, relevant waveforms and expressions.                                                                                                                                                                                                                                                   | 10 |

| 5.        | (a) Explain with neat diagram the static rotor resistance control method for the speed control of 3 phase induction motor.                                                                                                                                                                                                                                                                              | 10 |

|    | (b) Explain the effect of source inductane on the performance of a single phase fully controlled converter and derive the expression for the output voltage. | 10 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7. | Write short notes on (any two):—  (a) Control strategies employed in chopper for operating the switches.                                                     | 6  |

|    | (b) IR compensation                                                                                                                                          | 7  |

|    | ` <i>'</i> .                                                                                                                                                 | 7  |

|    | (c) Mc Murry inverter.                                                                                                                                       | /  |

|    |                                                                                                                                                              |    |

B.E. - Electronica. Sim VII Per Miselen Commo 27/11/2014 QP Code: 15351 (3 Hours) Total Marks: 100 Question No. 1 is compulsory. Solve any four questions out of remaining six questions. Figures to the right indicate full marks. Solve one complete question together. Explain the need of RAKE receiver in multipath propagation. Differentiate between soft hand-off and hard-hand off. (b) Draw and explain block diagram for OFDM. (c) Differentiate between IS-95 CDMA and CDMA 2000. (d)Draw and explain GSM frame structure in detail. 10 Explain the different techniques to improve coverage area and capacity in mobile 10 (b) communication. Draw and explain CDMA 2000 layered structure. 10 Explain power control mechanism in IS-95 system. 10 (b) Draw block diagram for signal processing in GSM. Explain it in detail. 4. 10 Differentiate between dynamic and fined channel assignment technique. (b) Define Grade of service and traffic in intensity related to trunking theory. (c) With the help of block diagram, explain direct sequence spread spectrum. 10 With the help of block diagram explain forward IS-95 CDMA system. 10 (b) Explain different physical and logical channels in IS-95 system. 10 6. (a) Draw and explain GSM system architecture in detail. 10 7. Write short notes on (any two):— Security in GSM. 10 (a)

10

10

Zigbee Network.

(b)

(c)

Data services in CDMA 2000

Elective II Election in 27/11/2014 Digital Image Processing by 8km

SCW VII

QP Code:15360

(3 Hours)

[ Total Marks: 100

N.B: (1) Question No. 1 is compulsory.

- (2) Out of the remaining questions attempt any four.

- (3) Figures in the right indicate maximum marks.

- 1. Answer any four:

- (a) Differentiate between spatial and tonal resolutions.

(b) Why is the sum of coefficients of a high pass filter mask zero?

- (c) Compare Huffman coding and arithmetic coding,

- (d) Give 3x3 masks for Laplacian filter, horizontal, vertical, +45° and -45° line detectors.

- (e) Explain dilation and erosion in brief.

- 2. (a) Explain the following enhancement operations and draw the graph of transformation 10 function:

- (i) Clipping, (ii) Bit plain slicing

- (b) Perform histogram equalization on the following image histogram and plot original and equalized histograms.

| Gray Level       | 0   | 1   | 2   | 3   | 4   | 5 | 6 | 7 |

|------------------|-----|-----|-----|-----|-----|---|---|---|

| Number of pixels | 200 | 300 | 500 | 350 | 250 | 0 | 0 | 0 |

3. (a) A source emits 6 symbols with the following probabilities:

| Symbol      | A   | В   | C    | D    | E    | F    |

|-------------|-----|-----|------|------|------|------|

| Probability | 0.1 | 0.2 | 0.05 | 0.05 | 0.35 | 0.25 |

Construct the Huffman code. Calculate the average code word length and coding efficiency.

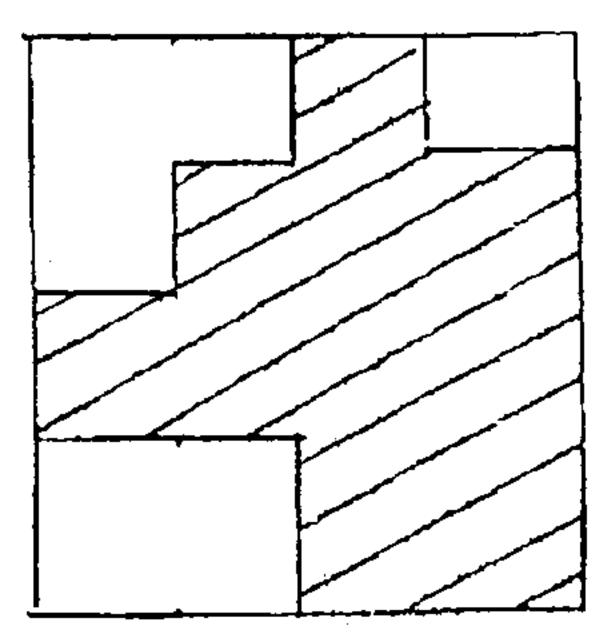

(b) Perform region splitting and merging on the image segment shown below. Draw the quad tree. Briefly explain the method used.

TURN OVER

4. (a) Calculate the Hadamard transform of the image segment,

$$f(x,y) = \begin{bmatrix} 2 & 3 & 1 & 4 \\ 2 & 1 & 1 & 4 \\ 1 & 3 & 4 & 4 \\ 3 & 3 & 2 & 2 \end{bmatrix}$$

- (b) State and prove any two properties of 2DDFT.

- (c) Obtain the 16 basis images of Hadamard transform.

- 5. (a) Given the 8 x 8 image segment, perform erosion using the structuring element shown:

| <b></b>  | <del>-,</del> - | <del> </del> |   |     |   |   |   |

|----------|-----------------|--------------|---|-----|---|---|---|

| 1        | 0               | 0            | 0 | 0   | 0 | 0 | 1 |

| 1        | 1               | 0            | 0 | 0   | 0 | 1 | 1 |

| 1        | 1               | 1            | 0 | 0   | 1 | 1 | 1 |

| 1        | 1               | 1            | 1 | 1   | 1 | 1 | 1 |

| 1        | 1               | 1            | 1 | 1   | 1 | 1 | 1 |

| 1        | 1               | 1            | 0 | 0 · | 1 | 1 | 1 |

| 1        | 1               | 0            | 0 | 0   | 0 | 1 | 1 |

| 1        | 0               | 0            | 0 | 0   | Ù | 0 | 1 |

| <u> </u> | <u> </u>        | L            |   |     |   |   |   |

Structuringelemen: 1 1 1

- (b) With the help of a neat block diagram, explain the working of the homomorphic 10 filter.

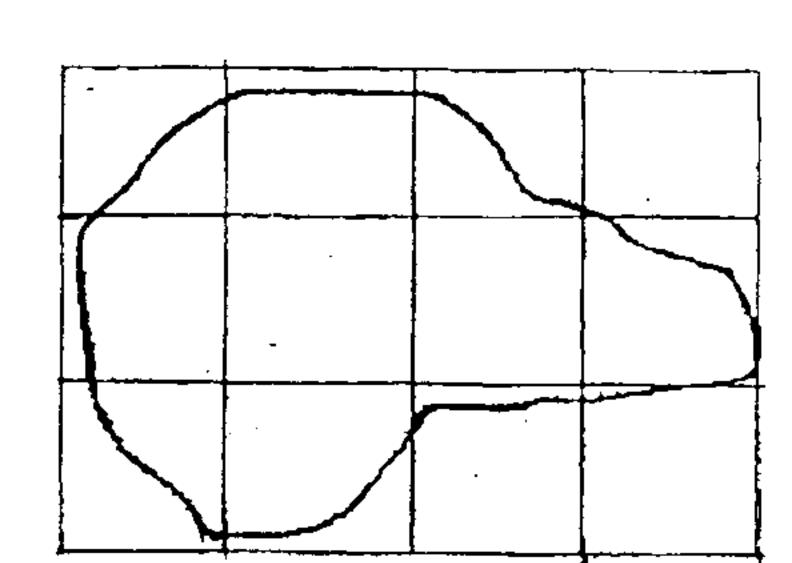

- 6. (a) What are chain codes? Obtain 4 connected and 8 connected chain codes for the boundary shown below:

|    | (b) Explain in detail different types of data redundancies present in the digital images. | 10 |

|----|-------------------------------------------------------------------------------------------|----|

| 7. | Write short notes on any four of the following:                                           | 20 |

|    | (a) Opening and closing                                                                   |    |

|    | (b) Color models                                                                          |    |

|    | (c) Finger print recognition                                                              |    |

|    | (d) Digital water marking                                                                 |    |

|    | (e) Handwritten character recognition.                                                    |    |

|    |                                                                                           |    |

|    |                                                                                           |    |

Sem VII Revi

15257

# Techia MS

97-11-2014 QP Code: 15357

|     |               | (3 Hours) [Total Marks: 100                                                                                                                                                                                |    |

|-----|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| N.E | <b>3</b> :(1) | Question No 1 is compulsory.                                                                                                                                                                               |    |

|     | (2)           |                                                                                                                                                                                                            |    |

|     | (3)           | Draw neat diagram wherever necessary.                                                                                                                                                                      |    |

| 1.  | (a)           | Explain organization of data cache of Pentium processor and explain why it is triple ported.                                                                                                               | 10 |

|     | · /           | Explain how are interrupts routed in PCI bus? Give suitable example. Also explain use of Interrupt Pin register and Interrupt Line register.                                                               | 10 |

| 2.  | ` '           | Explain instruction paring rules in Pentium processor.                                                                                                                                                     | 10 |

|     | (b)           | Explain how coherency is maintained between L1 data cache of Pentium Processor, L2 cache and main memory.                                                                                                  | 10 |

| 3.  | (a)           | Explain with a neat diagram data bus steering while executing 32 bit data read instruction. Assume 16 bit device interfaced to Pentium processor. Indicate how many bus cycles are run for this operation. | 12 |

|     | (b)           | Explain following signals in Pentium Processor INIT, LOCK#, SCYC, R/S#                                                                                                                                     | 8  |

| 4.  | (a)           | Explain with neat diagram protocol for PIO read command in IDE.                                                                                                                                            | 10 |

|     | (b)           | Explain the difference between synchronous and asynchronous data phase in SCSI.                                                                                                                            | 10 |

| 5.  | (a)           | Explain the process of Device Enumeration in USB devices.                                                                                                                                                  | 10 |

|     | (b)           | Explain Following signals in SCSI ATN, MSG, BSY, REQ, ACK                                                                                                                                                  | 10 |

| 6.  | (a)           | Master A wants to perform 2 transactions as 2 data writes from device C, 2 data reads from device D                                                                                                        | 12 |

|     |               | Master B wants to perform 3 data reads from device D                                                                                                                                                       |    |

|     |               | Master A & B request together, and priority of master B is less than that of A.                                                                                                                            |    |

|     | (b)           | Explain transactions performed with timing diagrams.  Explain bus parking in PCI bus.                                                                                                                      | 8  |

|     | (b)           | Explain ous parking in recrous.                                                                                                                                                                            | O  |

| 7.  | (a)           | Explain Reflected wave switching used in PCI bus.                                                                                                                                                          | 5  |

|     | (b)           | Explain the use of Branch Target Buffer in Pentium processor.                                                                                                                                              | 5  |

|     | (c)           | Explain methods of invalidating cache lines for Pentium processor.                                                                                                                                         | 5  |

|     | (d)           | Explain different data transfer types in USB.                                                                                                                                                              | 3  |

711ter Desi

21/11/2014

ETRX

QP Code: 15285

(3 Hours) |Total Marks: 100 N.B.: (1) Question No. 1 is compulsory. Attempt any four from remaining questions. Figures to the right indicate full marks. Assume suitable data if necessary. Attempt any four from following:— 20 (a) State the concept of adaptive filter (b) Explain quadrature mirror filtering in multirate DSP (c) Write a short note on prewarping. (d) Explain the principle of switched capacitor filter (e) Compare FIR and IIR filter Explain Gibb's phenomenon. State its significance in FIR filter design. 10 What is FDNR? State its properties. Explain synthesis of low pass functions using FDNR. Apply bilinear transformation to convert  $H(s) = \frac{2}{(s+1)(s+2)}$  to H(z) with T=1 sec. 10 Explain the effect of decimation and interpolation in time and frequency domain. 10 Design analog chebyshev filter with maximum passband attenuation of 3 dB at  $\Omega p = 200 \text{ rad/sec}$  and stopband attenuation of 60 dB at  $\Omega s = 1500 \text{ rad/sec}$ . Design low pass FIR linear phase filter with 11 coefficients by using Hamming window 10 for following specifications: Passband frequency: 0.25 KHz Sampling frequency: 1 KHz Explain leap frog realization technique with suitable example. (b) State working principle of Weiner filter. Explain the concept of subband coding.

6. (a) Design digital FIR filter with

$$H_{d}(e^{jw}) = e^{-j3w} \text{ for } -\frac{\pi}{4} \le |w| \le \frac{\pi}{4}$$

$$= 0 \qquad \text{for } \frac{\pi}{4} \le w \le \pi$$

Use Blackman window with N = 7.

- (b) Determine the order and poles of Lowpass Butterworth filter that has a 3 dB attenuation 10 at 500 Hz and attenuation of 40 dB at 1000 Hz.

- 7. Write short notes on:

Д

- (a) Why antialising /antiimaging required

- (b) What is inductance simulation? Explain

- (c) MMSE criteria in adaptive filters

- (d) Matched Z transform

## B.E. ETRX sem VII (R)&(Old), 9/12/14, VLSI Design

#### QP Code:15487

| <b>.</b> . |             | (3 Hours)                                                                                                                                 | Total Marks:    | 100 |

|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|

| N.         |             | 1) Question No. 1 is compulsory. 2) Attempt any four questions from remaining six questions.                                              |                 |     |

|            | ,           | 3) Assume suitable data wherever necessary.                                                                                               |                 |     |

|            | (           | 4) Figures to the right indicate marks.                                                                                                   |                 |     |

| 1.         | (a)         | Draw a energy band diagram of MOS capacitor under externa                                                                                 | l bias.         | 5   |

|            |             | Compare buried and butting contact                                                                                                        |                 | 5   |

|            | (c)         | Implement following function using CMOS.                                                                                                  |                 | 5   |

|            | (d)         | F = a.b + c.d + e<br>Draw the stick diagram for CMOS NOR gate.                                                                            |                 | 5   |

| 2.         | (a)         | Explain the various parameter affecting the threshold voltage                                                                             | •               | 10  |

|            | (h)         | Explain the effect of ion implantation on threshold voltage of                                                                            |                 |     |

|            | (0)         | Explain the complete fabrication process steps for CMOS line well process with the help of cross sectional diagram with all respectively. | $\sim$          | 10  |

| 3.         | (a)         | A CMOS symmetric inverter has following parameter                                                                                         |                 | 10  |

|            |             | $V_{DD} = 3.3 \text{ V}, V_{tn} = 0.6 \text{ V}, V_{tp} = -0.7 \text{ v}.$<br>$k_n = 200  \mu\text{A/V}^2  k_p = 80  \mu\text{A/V}^2$     |                 |     |

|            |             | $K_n = 200 \mu A/V^2 K_p = 80 \mu A/V^2$<br>Calculate noise margin of the circuit.                                                        |                 |     |

|            | (b)         | Define scaling. Discuss the advantages and disadvantages of different t                                                                   | vnes of scaling | 10  |

|            | • •         |                                                                                                                                           | pos or sounis.  | 10  |

| 4.         | (a)         | Draw circuit diagram, stick diagram and layout for two input No CMOS design rules.                                                        | OR gate using   | 10  |

|            | (b)         | Explain the operation of CMOS inverter with clearly mention                                                                               | ning the five   | 10  |

|            |             | cases given below.                                                                                                                        |                 |     |

|            |             | (i) $V_{in} < V_{tn}$ (ii) $V_{in} = V_{IL}$<br>(iii) $V_{in} = V_{IH}$ (iv) $V_{in} > V_{DD} + V_{tp}$                                   |                 |     |

|            |             | (v) $V_{in} = V_{TH}$ (Inverter threshold)                                                                                                |                 |     |

| 5.         | (a)         | Write a verilog code for 4 bit ripple counter using D-FF as a basi                                                                        | c component     | 10  |

|            |             | Compare passive load, active load NMOS inverter circuit wit                                                                               | •               | 10  |

|            |             | and disadvantages.                                                                                                                        |                 |     |

| 5.         | (a)         | Implement following boolean function using CMOS logic                                                                                     | •               | 10  |

|            |             | y = x.y.z + x.w.y                                                                                                                         |                 |     |

|            |             | Draw stick diagram and layout of the circuit.  What is latch up in CMOS inverter and how to avoid it                                      |                 |     |

|            | (0)         | What is latch up in CMOS inverter and how to avoid it.                                                                                    |                 | 10  |

| 7          | Wri         | te short notes on any three:-                                                                                                             |                 | 20  |

|            |             | Hot electron effect                                                                                                                       | •               |     |

|            |             | Y-chart for design flow                                                                                                                   |                 |     |

|            | (c)<br>(d)  | Design rules and their necessity Oxidation                                                                                                | •               |     |

|            | <b>(4</b> ) | LM-Con.:                                                                                                                                  | 10475-14.       |     |

BE. SEM VIII (Rev) - CN (E1R+) 15 Dec 2014

QP Code:156000

|               |                                                                                                                   |                                                                                   | (3 Hours)                                                                                  | [Total Marks:                                                                                    | 100      |

|---------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------|

|               | (2) An                                                                                                            |                                                                                   | ipulsory. of the remaining six h sketches wherever                                         | <b>→</b>                                                                                         |          |

| 1. An         | <ul> <li>(a) Co</li> <li>fib</li> <li>(b) Ex</li> <li>(c) Wh</li> <li>and</li> <li>(d) Ex</li> <li>net</li> </ul> | er optic transmission plain various LAN hat is meant by 'block demerits of a sing | ance characteristics of on media. topologies. king' in switched netwale stage space divisi | of co-axial, twisted pair and works? Bring out the merits on switch. control in Packet switching |          |

| 2. (a)<br>(b) | What i                                                                                                            | s Flow control? E                                                                 |                                                                                            | and message switching.<br>low flow control with neat                                             | 10<br>10 |

| 3. (a) (b)    | •                                                                                                                 | n in detail O.S.I. mo<br>DSL technology? E                                        |                                                                                            | hnologies and compare them.                                                                      | 10<br>10 |

| •             | SONE? With re                                                                                                     | T frames. Explain the ference to HDLC, warious frames of                          | he functional layers Explain the following HDLC.                                           | •                                                                                                | 10       |

|               | (ii)                                                                                                              | Data transfer mod                                                                 | ies.                                                                                       |                                                                                                  |          |

5. (a) Explain the different ARQ techniques in detail and state which ARQ technique 8 is preferred for noisy links? And why?

Unbalanced and balanced configuration.

- (b) Design a three stage Space division switch with N = 15, n = 5, K = 3 and 6 show how Blocking occurs in this. Derive the condition required to make this switch non-Blocking.

- (c) Discuss various Routing strategies for packet switching networks.

TURN OVER

Data transparency.

Piggy backing and Pipelining.

| 6. | (a) | Expla  | ain the following network connecting devices:—                  | 10 |

|----|-----|--------|-----------------------------------------------------------------|----|

|    | ` ' | _      | (i) switches (ii) routers (iii) gateway (iv) hub (v) bridge.    |    |

|    | (b) | Expla  | in the MAC sublayer Frame format for IEEE802 Reference? Explain | 10 |

|    |     | Fast   | Ethernet specifications. Also explain CSMA-CD in detail.        |    |

| 7. | Wri | te sho | t notes on :—                                                   | 20 |

|    |     | (a)    | ISDN.                                                           |    |

|    |     | (b)    | Sub-netting and Super-netting with an example.                  |    |

|    | I   | (c)    | IP utilities.                                                   |    |

|    |     | (d)    | Token Re-insertion Strategies.                                  |    |

|    |     |        |                                                                 |    |