7/6/2011 Karu-upg ki-11 B.E ETRX VIII (Rev) Embedded System 4-lead Time Peogleanmin

Con. 3893-11.

#### (REVISED COURSE)

RK-4632

| di laba |        |   |

|---------|--------|---|

| 1.12    | Hours) | ì |

| 10      | Hours  | ŗ |

| 1       |        |   |

[Total Marks: 100

| N.B.: (1) Question No. 1 is comp | pulso | ry. |

|----------------------------------|-------|-----|

|----------------------------------|-------|-----|

- (2) Attempt any four from the remaining six questions.

- (a) Suggest various techniques used for inter process communication in an 15 embedded system with relevant examples. Also, explain strategies used for synchronization between processes.

- (b) With the help of a neat diagram, explain the different states a task can be in 5 and the transitions between them.

- 2. (a) Explain the various operating modes of the ARMY processor. 10

- (b) What is the Shard Data Problem? Explain various techniques to overcome 10 it. (With relevant examples).

- (a) Explain the interface of Alphanumeric LCD with any microcontroller of your 7 choice. (Draw neat diagram)

- (b) Write a detailed note on the CAN Bus explaining its features and protocol. 7

- (c) Differentiate between CISC and RISC processors.

- (a) What is interrupt latency in Embedded systems ? Suggest methods to reduce 10 latency.

- (b) Explain what is the Linear sequential model in Embedded software 10 development.

- (a) Explain the Register set of the MSPHZO RISC controller (working Registers, 10 SFRs, status Register etc.)

- (b) Write a detailed note on the THUMB mode of operation of the ARMY processor. 10

- (a) Explain Bounded and unbanded priority Inversion problem. Suggest methods 10 to overcome / minimise it.

- (b) Explain the various program modelling techniques used in Embedded system 10 design.

#### 7. Write short notes on :-

20

- (a) Watching Timer

- (b) Serial Peripheral Interface (SPI)

- (c) Different types of memories in Embedded systems

- (d) Digital Signal Controllers (DSCs).

## B.E ETRX VIII (Rev)

# Elective II: Advanced Networking Technologies RK-4642

Con. 3958-11.

#### (REVISED COURSE)

|     |        | (3 Hours) [7                                                                                                                                                                                                 | Total Marks : 1 | 100 |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|

| N   | l.B. : | <ol> <li>Question No. 1 is compulsory.</li> <li>Solve any four from remaining six questions.</li> <li>Figures to the right indicate full marks.</li> <li>Assume suitable data wherever necessary.</li> </ol> |                 |     |

| Q.1 | A)     | How do the layers of TCP/IP model correlate to the layers of OS model?                                                                                                                                       | I (5)           |     |

|     | B)     | Distinguish between the ATM and frame relay.                                                                                                                                                                 | (5)             |     |

|     | C)     | Explain in brief the various security threats.                                                                                                                                                               | (5)             |     |

|     | D)     | With the help of a neat sketch explain DWDM.                                                                                                                                                                 | (5)             |     |

| Q.2 | A)     | Compare and contrast Ubiquitous and Hierarchical access.                                                                                                                                                     | (10)            |     |

|     | B)     | Explain subnetting and supernetting.                                                                                                                                                                         | (10)            |     |

| Q.3 | A)     | Sketch the frame format of frame relay and explain address field<br>it provides congestion control and quality of service.                                                                                   | . How (10)      |     |

|     | B)     | What do you mean by access layer design? explain.                                                                                                                                                            | (10)            |     |

| Q.4 | A)     | Explain in detail Repeaters, Routers, Bridges and Switches.                                                                                                                                                  | (10)            |     |

|     | B)     | Give the SONET/SDH hierarchy in brief.                                                                                                                                                                       | (5)             |     |

|     | C)     | With a suitable sketch, explain ATM cell format for user-networ interface.                                                                                                                                   | k (5)           |     |

| Q.5 | A)     | Explain ATM adaptation layer also describe the concept of VPI vVCI.                                                                                                                                          | and (10)        | ň   |

|     | B)     | What is remote monitoring? Explain benefits of remote monitori                                                                                                                                               | ng. (5)         |     |

| - 1 | C)     | Write a short note on SONET hardware.                                                                                                                                                                        | (5)             |     |

| Q. | 6 A) | Discuss designing a network manag   | ement solution. |         | (10) |

|----|------|-------------------------------------|-----------------|---------|------|

|    | B)   | Describe network security safeguard | ls in detail.   |         | (10) |

|    |      | 16.                                 |                 | - 6     |      |

| Q. | 7    | Write short notes on:               |                 |         | (20) |

|    | A)   | IEEE 802.11                         | 4               | 1 a 2   |      |

|    | B)   | Internetworking protocols           | 221             |         | 47   |

|    | C)   | OAM & P                             |                 |         |      |

|    | D)   | Enterprise Network Security         | 1.0             |         |      |

|    |      |                                     |                 | illine. |      |

B F FTRX VIII (Rev)

Elective II - DSP Processors f

Architectures

RK-4635

Con. 3983-11.

Q7

Write short notes on:

a) FFT algorithm using a typical DSP.

b) Implementation of FIR/IIR filters on a DSP.

#### (REVISED COURSE)

(20)

(3 Hours)

[Total Marks: 100

|      |    | N.B.                            | 1        | Question No. 1 is compulsory.                                                        |                         |

|------|----|---------------------------------|----------|--------------------------------------------------------------------------------------|-------------------------|

|      |    | S. Carrier Tra                  | 2        | Out of the remaining questions attempt any 4 questions.                              |                         |

|      |    |                                 | 3        | All questions carry equal marks.                                                     |                         |

|      |    |                                 | :D:      | All questions carry equal marks.                                                     |                         |

| Q1   |    |                                 |          |                                                                                      |                         |

|      |    | With respect                    | to prog  | rammable digital signal processors in general, write a compr                         | ehensive note           |

|      |    | on the archit                   | ectural  | features covering the points of bus and memory structu                               | re, MAC unit,           |

|      |    | pipelining feat                 | ture, m  | ulti-ported memories etc.                                                            | (20)                    |

| Q2   |    |                                 |          |                                                                                      |                         |

| 23.0 | a) | With a neat                     | block (  | diagram explain the architecture of TMS320C5X processor.                             | Highlight the           |

|      |    | functions of co                 | entral a | arithmetic logic unit (CALU) and auxiliary register ALU (ARAU).                      | (14)                    |

|      | b) | List the on-ch                  | ip peri  | pherals and their functions in TMS320C5X processor.                                  | (06)                    |

| Q3   |    |                                 |          |                                                                                      |                         |

|      | a) | With the help                   | of exa   | mples explain the various addressing modes of CSX processor                          | (14)                    |

|      | b) | Explain briefly                 | the ac   | dition and subtraction instructions in C5X processor.                                | (06)                    |

| Q4   |    |                                 |          |                                                                                      |                         |

| 3000 | a) |                                 |          | tural features of ADSP 21xx series of digital signal processors.<br>MS320C5X series. | Compare the             |

|      | b) | How does the                    | clock    | (crystal) speed affect the system through-put in a typical co                        | ntroller based          |

|      |    | system? What<br>speeds for rec  |          | he techniques used by designers to retain high through-put a<br>EMI.                 | t lower crystal<br>(06) |

| Q5   |    |                                 |          |                                                                                      |                         |

|      | a) | Discuss the ar                  | chitect  | ural features of TMS320C6X digital signal processor and com-                         | pare the same           |

|      |    | with DSP563X                    | X from   | Motorola.                                                                            | (14)                    |

|      | b) | What is the no<br>with switched |          | high speed, high resolution ADC and DAC in digital signal pro<br>itor filters?       | cessors along-<br>(06)  |

| Q6   |    |                                 |          | · · · · · · · · · · · · · · · · · · ·                                                |                         |

|      | a) |                                 |          | e on the pipelining operation in C5X series of digital signal pr                     | 77                      |

|      |    |                                 |          | e instruction examples.                                                              | (14)                    |

|      | b) | List the on-ch<br>processors.   | iip per  | ipherals and their functional requirements in C5X series of                          | digital signal<br>(06)  |

BE ETRX VIII (Per)

Robotics & dulomation

ris-Scan Pager -1 (

Con. 3840-11.

C. Template Matching.

### (REVISED COURSE)

RK-4629

(3 Hours)

N.B.: 1) 'Question No. 'One 'is compulsory.

[Total Marks: 100

|    |    | <ol> <li>Attempt any 'four' out of remaining 'six'.</li> <li>Figures to right indicate full marks, 'all' questions carry equal marks.</li> <li>Assume suitable data wherever necessary.</li> </ol>  |    |

|----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1  |    | Answer the following questions;                                                                                                                                                                     |    |

|    | A. | Define the following terms: Tool Path, Tool Trajectory, DOF, Precision, Accuracy                                                                                                                    | 05 |

|    | В. | Explain the properties of inverse kinematics solution.                                                                                                                                              | 05 |

|    | C. | Define kinematic parameters. What is soft home configuration?                                                                                                                                       | 05 |

|    | D. | Draw symbols of Input and Output devices and Switches used in ladder diagrams.                                                                                                                      | 05 |

| 2  | Α. | Compare Hard Automation and Soft Automation. State advantages and drawbacks of each.                                                                                                                | 10 |

|    | B. | Explain the screw transformation. Show that the inverse of a screw transformation is again a screw transformation.                                                                                  | 10 |

| 3. | A. | Apply D-H algorithm for SCARA robot and construct a link-coordinate diagram. Compute the arm matrix for the SCARA Robot.                                                                            | 10 |

|    | В. | Define Tool-Configuration vector. Show how to obtain tool roll angle: What are the advantages/disadvantages of Numerical approach and Analytical approach to solve the Inverse kinematics problems? | 10 |

| 4, | A. | Explain the shrink and swell operators with an example. How are they applied? List all the properties of these operators.                                                                           | 10 |

|    | В. | Explain the 4 point minimal PNP trajectory for pick and place of objects by using a robot manipulator                                                                                               | 10 |

| 5. | A. | What is a GVD? Sketch all the GVD's resulting due to the basic interactions of the obstacles .Derive the necessary equations.                                                                       | 10 |

|    | В. | Explain in details block diagram of PLC(Programmable Logic controller), Hence write ladder diagram programs to Implement Logic functions AND, OR, NOT, NAND, NOR                                    | 10 |

| 6, | A. | Obtain Direct kinematics solution of three axis planer articulated robot arm.                                                                                                                       | 10 |

|    | B. | Write specifications of PLC                                                                                                                                                                         | 05 |

|    | C. | Write Industrial Applications of PLC                                                                                                                                                                | 05 |

| 7. |    | Write short notes on (Any Two);                                                                                                                                                                     | 20 |

|    | A. | Perspective Transformation                                                                                                                                                                          |    |

|    | B  | Workspace Fixtures                                                                                                                                                                                  |    |

# BE ETRX - TITT (R) Advance vals i design

Con. 3263-11.

#### (REVISED COURSE)

RK-4644

(3 Hours)

[Total Marks: 100

N.B.: (1) Question No. 1 is compulsory.

- 2) Attempt any four out of remaining six questions.

- 3) Assume any suitable data wherever required but justify the same.

- 1. a. Determine intrinsic gate capacitance with  $t_{ox}{=}~150A^0~,~\epsilon_{0x}{=}~3.9~x8.85x10^{-14}~F/cm~,~~and~~V_G{=}3.3~Volts$  if W=4  $\mu m$  L=2 $\mu m$

- Explain the need of interconnect delay model? Also define Cross-talk in case of VLSI design.

- c. Explain the factors on which dynamic power dissipation depends?

- d. Explain the parameters to be taken care while design of the adder circuit.

- e. Draw the analog design octagon and explain its significance.

- a. Explain how process variation can cause variation in speed? Explain the concept of Design Corner.

- b. Draw the schematic of Carry look ahead adder explain how the speed can 10 be improved?

- 3. a. What are the issues of clock distribution? Explain how they are addressed? 10 Also explain how the cross-talk in multilayer system is modeled?

- b, State the need of Input and Output circuit? Explain with neat diagram the 10 schematic and design consideration for the same.

- a. Implement the following function using NOR-NOR implementation for a 10 PLA

- i. Y<sub>1</sub>=ac+b'c

- ii. Y2= abc+-a'b'c

- iii. Y3=-a'b + ab

- b. Explain the clock generation and different types of clocking schemes for 10 VLSI circuit Explain what do you mean by clock skew and clock jitter and how it can be estimated

f TURN OVER

| 5. | а, | Find | resistance Rn for nMOS if electron mobility $\mu_n = 560 \text{cm}^2/\text{V-sec}$                                    | 10 |

|----|----|------|-----------------------------------------------------------------------------------------------------------------------|----|

|    |    |      | $t_{ox}\!\!=10$ nm , $\epsilon_{0x}\!\!=3.9~x8.85x10^{-14}~F/cm$ , and $V_G\!\!=\!\!3.3~Volts$                        |    |

|    |    |      | V <sub>THe</sub> =0.7 Volts                                                                                           |    |

|    |    |      | i) if W=10µm L=0.5µm                                                                                                  |    |

|    |    |      | <ul> <li>ii) if channel width is increased to a value of W=22μm while the<br/>channel length remains same.</li> </ul> |    |

|    |    | Ь.   | Explain how propagation delay caused by distributed Resistance-                                                       | E  |

|    |    | 4    | Capacitance (RC) in the long wire can be reduced? Derive the expression                                               | 10 |

|    |    |      | to neglect the wire-length delay with respect to gate delay                                                           |    |

|    | 6, | а.   | Explain the three knobs on the basis by which CMOS designer optimize the                                              | 10 |

|    |    |      | speed of CMOS gate Explain how to approximate calculation of power                                                    |    |

|    |    |      | dissipation at increasing accuracy                                                                                    | 10 |

|    |    | b.   | State the need and various applications of analog VLSI circuit design. Why                                            |    |

|    |    |      | analog circuit design is is difficult as compare to digital design?                                                   |    |

|    | 7. |      | Write a short note on (any four):                                                                                     | 20 |

|    |    | a.   | Charge sharing and transistor sizing.                                                                                 |    |

|    |    | b.   | Different clock system                                                                                                |    |

|    |    | c.   | The role of sense amplifier                                                                                           |    |

|    |    | d.   | Flash cell construction and working                                                                                   |    |

|    |    | e.   | Telescopic cascade op-amps                                                                                            |    |

|    |    | f.   | Switched capacitor Amplifier                                                                                          |    |

|    |    |      |                                                                                                                       |    |

46 : 1st half 11-AM(n)

Con. 3771-11.

#### (REVISED COURSE)

**RK-4638**

(3 Hours)

[Total Marks: 100

N.B.: (1) Question No. 1 is compulsory.

- (2) Attempt any four question out of remaining six questions.

- (3) Assumption made must be clearly stated.

- Solve any four of the following:

20

- Show that any λ-cut relation (for λ > 0) of a Fuzzy tolerance relation results in a crisp tolerance relation.

- (b) Explain common activation function used in neural network.

- (c) Distinguish between Supervised and Unsupervised Training.

- (d) Compare LMS and Perceptron Learning Laws.

- (e) Explain Delta learning rule.

- (f) What are the salient features of Kohonen's self-organizing learning algorithm?

- 2. (a) State and explain the basic learning laws.

10

- (b) Explain perceptron learning rule convergence theorem. Design a perceptron 10 network to implement an AND function, take first input sample [1, 1, 1]

- 3. (a) Derive the back propagation training algorithm for an arbitrary activation function. 8

- (b) How can you approximate a Gaussian function by two sigmoid function? How can you translate a radial basis function network in to a back propagation network?

- (c) How do we achieve fast learning in ART 2 network?

4

- (a) What is the Hopfield model of a neural network? Explain its algorithm and 10 differentiate between discrete and continuous Hopfield model in terms of energy landscape and stable state.

- (b) Two Fuzzy sets A define on X and B define on Y

10

$$\underline{A} = \left\{ \frac{1}{LS} + \frac{0.4}{MS} + \frac{0.2}{HS} \right\}$$

$$\underline{B} = \left\{ \frac{1}{SRR} + \frac{0.5}{MRR} + \frac{0.25}{FRR} \right\}$$

- (i) Find the Fuzzy relation for Cartesian product of A and B

- (ii) For another Fuzzy set ∑ define on X

$$\mathbf{C} = \left\{ \frac{0 \cdot 1}{LS} + \frac{0 \cdot 3}{MS} + \frac{1}{HS} \right\}$$

Find relation between C and B using Cartesian product.

(iii) Find CoR using max-min and max-product composition.

- (a) Show that any λ-cut relation (For λ > 0) of Fuzzy tolerance relation results in a 10 crisp tolerance relation and any λ-cut relation (for λ > 0) of a Fuzzy equivalence relation results in a crisp equivalence relation.

- (b) What is self organizing map ? Explain structure and algorithm of Kohonen self 10 organizing map.

8

4

10

10

- 6. (a) Explain Brain-state-in-a-box model and explain how it is used for clustering? 8

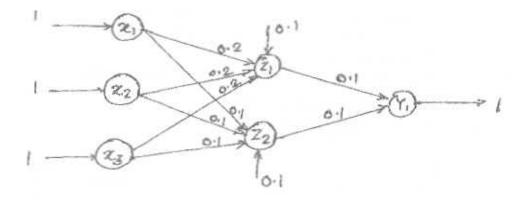

- (b) For the given network

Find new weights when net is presented the input pattern (1, 1, 1) and target output is '1'. Use learning rate of 0-1 and bipolar sigmoidal activation function, the bias is set to '1'.

Activation function:

$$f(x) = \frac{2}{1 + e^{-x}} - 1$$

and  $f'(x) = 0.5 (1 + f(x)) (1 - f(x))$

- (c) Explain Mc-culloch and pitts model of neuron.

- 7. (a) State and explain various method of defuzzification.

- (b) Write short notes on the following :-

- (i) Fuzzy Controller

- (ii) Least mean square algorithm.